Few days ago the Institute of Information Technology of the Chinese Academy of Sciences unveiled the project XiangShan, in which it has been developing since 2020 a high-performance open processor based on the RISC-V (RV64GC) instruction set architecture and whose performance approaches the speed of SiFive's latest Performance P550 core.

According to the developers, RISC-V cores underlying Xiangshan CPU will become so popular among designers of processors such as Linux for operating systems. Xiangshan will be manufactured using a 28nm process technology by Taiwanese TSMC (unless sanctions are imposed by the United States) and this will be the first generation of cores codenamed Yanqi Lake.

RISC-V provides an open and flexible machine instruction system that allows you to create microprocessors for arbitrary applications without requiring royalties or imposing conditions of use. RISC-V allows you to create completely open SoCs and processors.

Currently, based on the RISC-V specification, several companies and communities under various free licenses (BSD, MIT, Apache 2.0) are developing several dozen variants of already manufactured microprocessor cores, SoCs and chips.

About XiangShan

The project has been published under a description of hardware blocks in the Chisel language, which is translated into Verilog, a reference implementation based on FPGA and images to simulate the operation of a chip in an open Verilog simulator.

“Although our long-term goal going forward is to be in line with [Cortex-] A76, it is still in progress. We need down-to-earth iterative optimization. The purpose of agile development is not to overtake a corner. The experience accumulated by Intel and Arm over the years, we also have to accumulate slowly.

Schematics and architecture descriptions are also available (more than 400 documents and 50 thousand lines of code in total), but most of the documentation is in Chinese, plus Debian is used as a reference operating system to test the FPGA implementation.

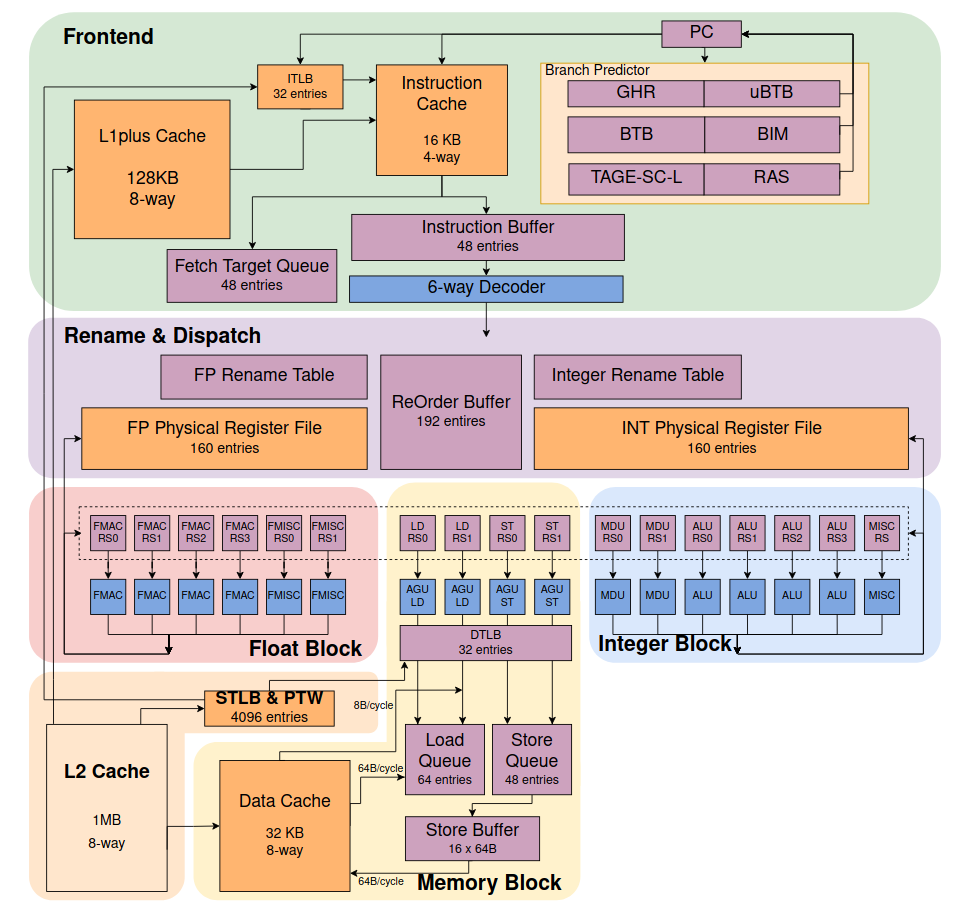

XiangShan claims to be the highest performing RISC-V chip, outperforming the SiFive P550. FPGA testing is scheduled to be completed this month and the code name "Yanqi Lake" is an 8-core prototype chip that operates at 1,3 GHz and is manufactured at TSMC using process technology from 28 nm.

"We are hopeful that XiangShan can survive for 30 years," Bao said, translated, in a recent presentation on the project. “We have an agreement to meet again in 30 years and then see what XiangShan will become. However, to realize this wish, there are still many problems and challenges that must be solved.

The chip includes a 2MB cache, a memory controller with support for DDR4 memory (up to 32 GB of RAM) and a PCIe-3.0-x4 interface.

The performance of the first chip in the SPEC2006 benchmark is estimated at 7 / Ghz, which corresponds to the ARM Cortex-A72 and Cortex-A73 chips.

"The agile design process and platform we built previously support a development team of more than 20 people, which is far from sufficient," said Bao. "What we need to consider now is how to build a set of standardized, open and open source open processes that can support the development of an open source community of 2000 people."

Production of a second prototype is planned for the end of the year "South Lake" with an improved architecture, which will be produced by SMIC with a process technology of 14nm and a frequency increase to 2 GHz.

The second prototype is expected to achieve a performance of 10 / Ghz on the SPEC2006 benchmark, which is close to the ARM Cortex-A76 and Intel Core i9-10900K processors, and outperforms the SiFive P550, the fastest RISC-V CPU at 8.65 / Ghz.

Finally, if you are interested in knowing more about it, you can consult the source code of XiangShan, which has been published under the MulanPSL2, on GitHub.

Source: https://www.zhihu.com

They are overly optimistic even though it is still being tested and given the fact that most of the documentation is in Chinese when they found it in English. However, I agree that the future will be RISC-V.