ไม่กี่วันที่ผ่านมา สถาบันเทคโนโลยีสารสนเทศแห่งสถาบันวิทยาศาสตร์จีนเปิดตัว โครงการ XiangShan ซึ่งได้รับการพัฒนามาตั้งแต่ปี 2020 โปรเซสเซอร์แบบเปิดประสิทธิภาพสูงที่ใช้สถาปัตยกรรมชุดคำสั่ง RISC-V (RV64GC) และประสิทธิภาพใกล้เคียงกับความเร็วของคอร์ Performance P550 ล่าสุดของ SiFive

ตามที่นักพัฒนากล่าวว่า แกน RISC-V ที่เป็นพื้นฐานของ Xiangshan CPU จะได้รับความนิยมอย่างมาก ในบรรดาผู้ออกแบบโปรเซสเซอร์เช่น Linux สำหรับระบบปฏิบัติการ Xiangshan จะผลิตโดยใช้เทคโนโลยีการผลิต 28nm โดย TSMC ของไต้หวัน (เว้นแต่จะมีการคว่ำบาตรโดยสหรัฐอเมริกา) และนี่จะเป็นแกนรุ่นแรกที่มีชื่อรหัสว่า Yanqi Lake

RISC-V มีระบบการเรียนการสอนเครื่องที่เปิดกว้างและยืดหยุ่น ที่ช่วยให้คุณสร้างไมโครโปรเซสเซอร์สำหรับแอปพลิเคชันโดยพลการโดยไม่ต้องมีค่าลิขสิทธิ์หรือกำหนดเงื่อนไขการใช้งาน RISC-V ช่วยให้คุณสร้าง SoC และโปรเซสเซอร์แบบเปิดได้อย่างสมบูรณ์

ปัจจุบัน ตามข้อกำหนดของ RISC-V บริษัทและชุมชนหลายแห่งภายใต้ใบอนุญาตฟรีต่างๆ (BSD, MIT, Apache 2.0) กำลังพัฒนาคอร์ไมโครโปรเซสเซอร์, SoC และชิปที่ผลิตขึ้นแล้วหลายสิบตัว

เกี่ยวกับ XiangShan

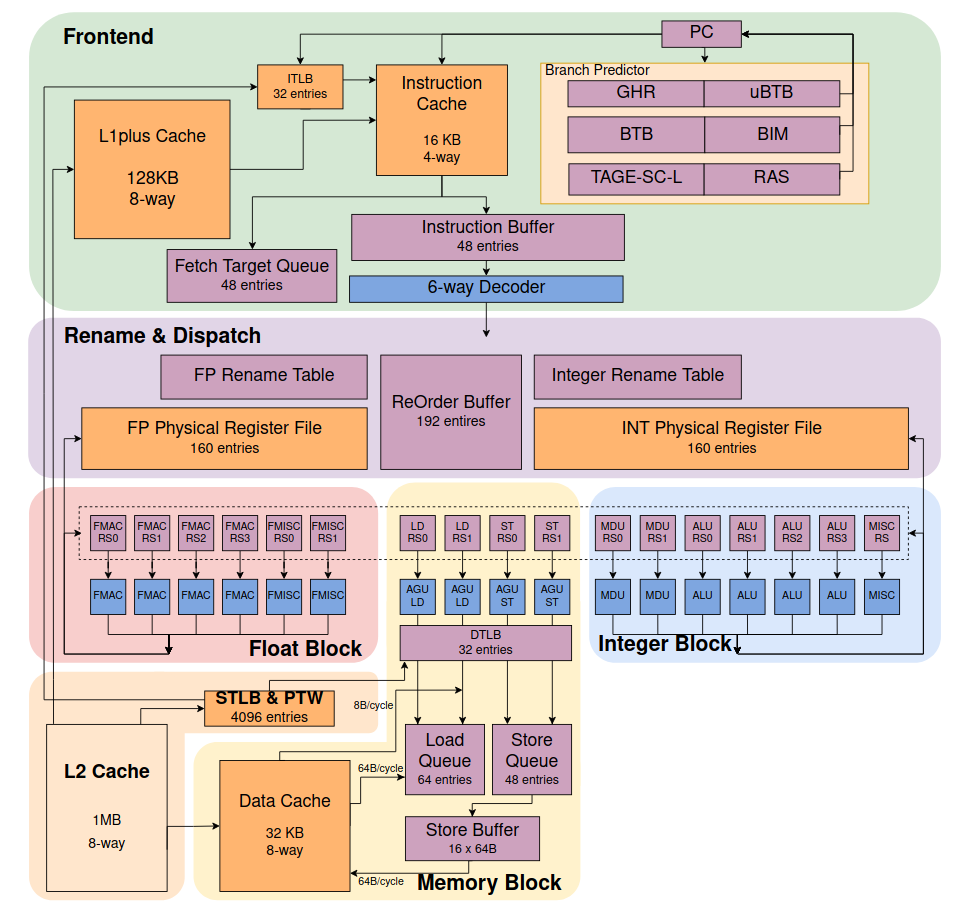

โครงการ ได้รับการตีพิมพ์ภายใต้คำอธิบายของบล็อคฮาร์ดแวร์ในภาษาสิ่วซึ่งแปลเป็น Verilog ซึ่งเป็นการใช้งานอ้างอิงตาม FPGA และรูปภาพเพื่อจำลองการทำงานของชิปในโปรแกรมจำลอง Verilog แบบเปิด

“แม้ว่าเป้าหมายระยะยาวของเราในอนาคตจะต้องสอดคล้องกับ [Cortex-] A76 แต่ก็ยังอยู่ในระหว่างดำเนินการ เราต้องการการปรับให้เหมาะสมแบบทำซ้ำลงสู่พื้นดิน จุดประสงค์ของการพัฒนาอย่างปราดเปรียวไม่ใช่เพื่อแซงโค้ง จากประสบการณ์ที่สั่งสมมาโดย Intel และ Arm ตลอดหลายปีที่ผ่านมา เราก็ยังต้องค่อยๆ สะสมไป

แผนผังและคำอธิบายสถาปัตยกรรมก็มีให้เช่นกัน (เอกสารมากกว่า 400 รายการและโค้ดทั้งหมด 50 บรรทัด) แต่เอกสารส่วนใหญ่เป็นภาษาจีน นอกจากนี้ Debian ยังใช้เป็นระบบปฏิบัติการอ้างอิงเพื่อทดสอบการใช้งาน FPGA

XiangShan อ้างว่าเป็นชิป RISC-V ที่มีประสิทธิภาพสูงสุด เหนือกว่า SiFive P550 การทดสอบ FPGA มีกำหนดจะแล้วเสร็จในเดือนนี้ และชื่อรหัส "Yanqi Lake" เป็นชิปต้นแบบ 8 คอร์ที่ทำงานที่ 1,3 GHz และผลิตขึ้นที่ TSMC โดยใช้เทคโนโลยีกระบวนการผลิตจาก นาโนเมตร 28.

“เราหวังว่าเซียงซานจะสามารถอยู่รอดได้เป็นเวลา 30 ปี” เปากล่าวในการนำเสนอเกี่ยวกับโครงการเมื่อเร็วๆ นี้ “เรามีข้อตกลงที่จะพบกันอีกครั้งใน 30 ปี จากนั้นรอดูว่าเซียงซานจะเป็นอย่างไร อย่างไรก็ตาม เพื่อให้เป็นไปตามความปรารถนานี้ ยังมีปัญหาและความท้าทายมากมายที่ต้องแก้ไข

ชิป รวมแคช 2MB, ตัวควบคุมหน่วยความจำด้วย รองรับหน่วยความจำ DDR4 (สูงสุด 32 GB of RAM) และอินเทอร์เฟซ PCIe-3.0-x4

ประสิทธิภาพของชิปตัวแรกในเกณฑ์มาตรฐาน SPEC2006 อยู่ที่ประมาณ 7 / Ghz ซึ่งสอดคล้องกับชิป ARM Cortex-A72 และ Cortex-A73

“ขั้นตอนการออกแบบและแพลตฟอร์มที่คล่องตัวที่เราสร้างขึ้นก่อนหน้านี้สนับสนุนทีมพัฒนาที่มีมากกว่า 20 คน ซึ่งยังไม่เพียงพอ” Bao กล่าว "สิ่งที่เราต้องพิจารณาในตอนนี้คือวิธีสร้างชุดของกระบวนการโอเพ่นซอร์สที่ได้มาตรฐาน โอเพ่นซอร์ส และโอเพ่นซอร์ส ที่สามารถรองรับการพัฒนาชุมชนโอเพ่นซอร์สจำนวน 2000 คน"

มีการวางแผนการผลิตต้นแบบที่สองในปลายปีนี้ "เซาท์เลค" ด้วยสถาปัตยกรรมที่ได้รับการปรับปรุงซึ่งจะผลิตโดย SMIC พร้อมเทคโนโลยีการผลิต 14nm และความถี่เพิ่มขึ้นเป็น 2 GHz

ต้นแบบที่สองคาดว่าจะบรรลุประสิทธิภาพ 10 / Ghz บนเกณฑ์มาตรฐาน SPEC2006 ซึ่งใกล้เคียงกับโปรเซสเซอร์ ARM Cortex-A76 และ Intel Core i9-10900K และมีประสิทธิภาพสูงกว่า SiFive P550 ซึ่งเป็น CPU RISC-V ที่เร็วที่สุดที่ 8.65 / Ghz

สุดท้ายนี้ หากคุณสนใจที่จะทราบข้อมูลเพิ่มเติม คุณสามารถศึกษาซอร์สโค้ดของ XiangShan ซึ่งได้รับการเผยแพร่ภายใต้ MulanPSL2 บน GitHub

Fuente: https://www.zhihu.com

พวกเขามองโลกในแง่ดีเกินไปแม้ว่าจะยังอยู่ระหว่างการทดสอบและเนื่องจากเอกสารส่วนใหญ่เป็นภาษาจีนเมื่อพบว่าเป็นภาษาอังกฤษ อย่างไรก็ตาม ผมเห็นด้วยว่าอนาคตจะเป็น RISC-V