Några dagar sen avslöjade institutet för informationsteknologi vid den kinesiska vetenskapsakademin projektet XiangShan, där den har utvecklats sedan 2020 en högpresterande öppen processor baserad på RISC-V (RV64GC) instruktionsuppsättningsarkitektur och vars prestanda närmar sig hastigheten för SiFives senaste Performance P550-kärna.

Enligt utvecklarna, RISC-V-kärnor som ligger till grund för Xiangshan CPU kommer att bli så populära bland designarna av processorer som Linux för operativsystem. Xiangshan kommer att tillverkas med en 28 nm processteknik av taiwanesiska TSMC (såvida inte sanktioner införs av USA) och detta kommer att bli den första generationen av kärnor med kodenamnet Yanqi Lake.

RISC-V tillhandahåller ett öppet och flexibelt maskininstruktionssystem som låter dig skapa mikroprocessorer för godtyckliga applikationer utan att kräva royalties eller införa villkor för användning. Med RISC-V kan du skapa helt öppna SoC: er och processorer.

För närvarande, baserat på RISC-V-specifikationen, utvecklar flera företag och samhällen under olika fria licenser (BSD, MIT, Apache 2.0) flera dussin varianter av redan tillverkade mikroprocessorkärnor, SoC och chips.

Om XiangShan

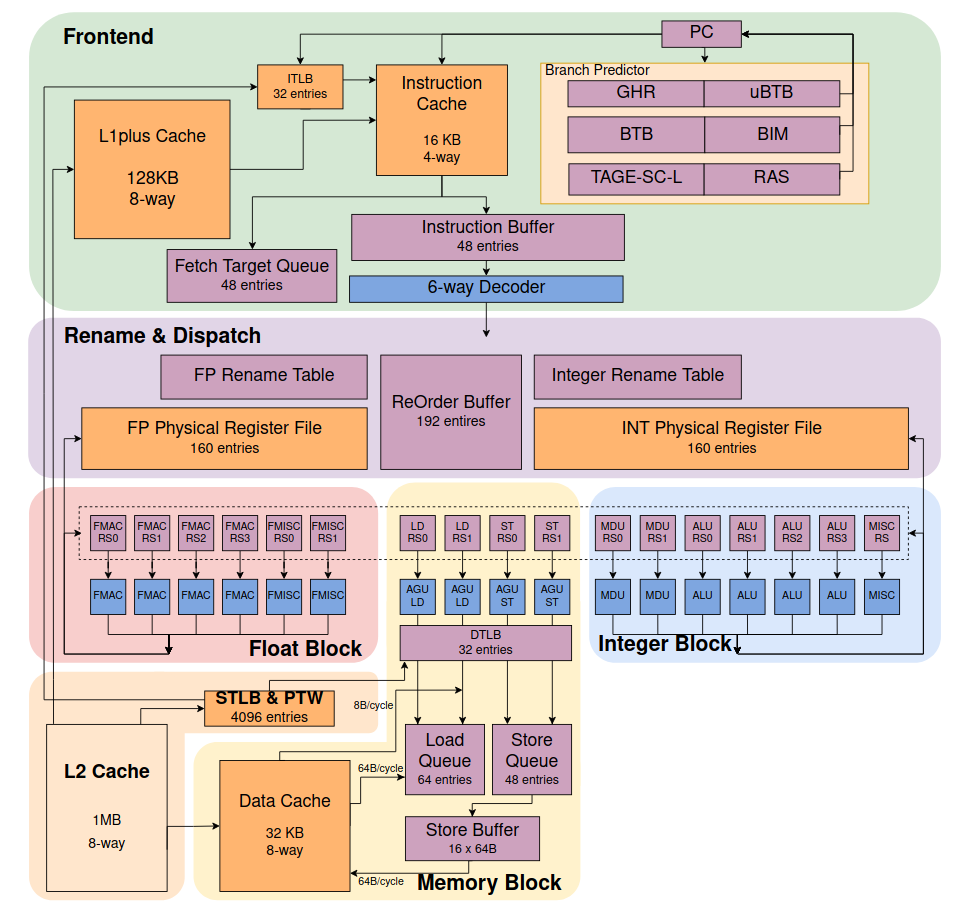

Projektet har publicerats under en beskrivning av hårdvarublock på mejsel-språket, som översätts till Verilog, en referensimplementering baserad på FPGA och bilder för att simulera driften av ett chip i en öppen Verilog-simulator.

”Även om vårt långsiktiga mål framöver är att vara i linje med [Cortex-] A76, pågår det fortfarande. Vi behöver jordnära iterativ optimering. Syftet med smidig utveckling är inte att ta ett hörn. Erfarenheten som ackumulerats av Intel och Arm genom åren, måste vi också ackumulera långsamt.

Scheman och arkitekturbeskrivningar finns också (mer än 400 dokument och 50 tusen rader kod totalt), men det mesta av dokumentationen är på kinesiska, plus Debian används som ett referensoperativsystem för att testa FPGA-implementeringen.

XiangShan hävdar att det är det RISC-V-chip som bäst presterar och överträffar SiFive P550. FPGA-tester är planerade att slutföras denna månad och kodnamnet "Yanqi Lake" är ett 8-kärnigt prototypchip som fungerar vid 1,3 GHz och tillverkas på TSMC med processteknik från 28 nm.

"Vi är hoppfulla att XiangShan kan överleva i 30 år," sa Bao, översatt, i en presentation om projektet nyligen. ”Vi har en överenskommelse att träffas igen om 30 år och sedan se vad XiangShan kommer att bli. Men för att förverkliga denna önskan finns det fortfarande många problem och utmaningar som måste lösas.

Chipet innehåller en 2 MB cache, en minneskontroll med stöd för DDR4-minne (upp till 32 GB RAM) och ett PCIe-3.0-x4-gränssnitt.

Prestandan för det första chipet i SPEC2006-riktmärket uppskattas till 7 / Ghz, vilket motsvarar ARM Cortex-A72 och Cortex-A73 chips.

"Den smidiga designprocessen och plattformen vi byggde stöder tidigare ett utvecklingsteam på mer än 20 personer, vilket är långt ifrån tillräckligt", säger Bao. "Vad vi behöver tänka på nu är hur man bygger en uppsättning standardiserade, öppna och öppen källkodsprocesser som kan stödja utvecklingen av en öppen källkodsgrupp med 2000 personer."

I slutet av året planeras produktionen av en andra prototyp "South Lake" med en förbättrad arkitektur, som kommer att produceras av SMIC med en processteknik på 14 nm och en frekvensökning till 2 GHz.

Den andra prototypen förväntas uppnå en prestanda på 10 / Ghz på SPEC2006-riktmärket, som ligger nära ARM Cortex-A76 och Intel Core i9-10900K-processorer, och överträffar SiFive P550, den snabbaste RISC-V-processorn på 8.65 / Ghz.

Slutligen, om du är intresserad av att veta mer om det, kan du konsultera källkoden för XiangShan, som har publicerats under MulanPSL2, på GitHub.

Fuente: https://www.zhihu.com

De är överdrivet optimistiska trots att det fortfarande testas och med tanke på att nästan all dokumentation är på kinesiska när de hittade den på engelska. Jag håller dock med om att framtiden kommer att vara RISC-V.