Acum cateva zile a fost dezvăluit Institutul de Tehnologia Informației al Academiei Chineze de Științe proiectul XiangShan, în care se dezvoltă din 2020 un procesor deschis de înaltă performanță bazat pe arhitectura setului de instrucțiuni RISC-V (RV64GC) și a cărui performanță se apropie de viteza celui mai recent core de performanță SiFive P550.

Potrivit dezvoltatorilor, Nucleele RISC-V care stau la baza procesorului Xiangshan vor deveni atât de populare printre proiectanții de procesoare precum Linux pentru sistemele de operare. Xiangshan va fi fabricat folosind o tehnologie de proces de 28nm de către TSMC taiwaneză (cu excepția cazului în care sancțiunile sunt impuse de Statele Unite) și aceasta va fi prima generație de nuclee cu numele de cod Lacul Yanqi.

RISC-V oferă un sistem de instrucțiuni mașină deschis și flexibil care vă permite să creați microprocesoare pentru aplicații arbitrare fără a necesita redevențe sau impunerea condițiilor de utilizare. RISC-V vă permite să creați SoC-uri și procesoare complet deschise.

În prezent, pe baza specificației RISC-V, mai multe companii și comunități sub diferite licențe gratuite (BSD, MIT, Apache 2.0) dezvoltă câteva zeci de variante de nuclee de microprocesor deja fabricate, SoC-uri și cipuri.

Despre XiangShan

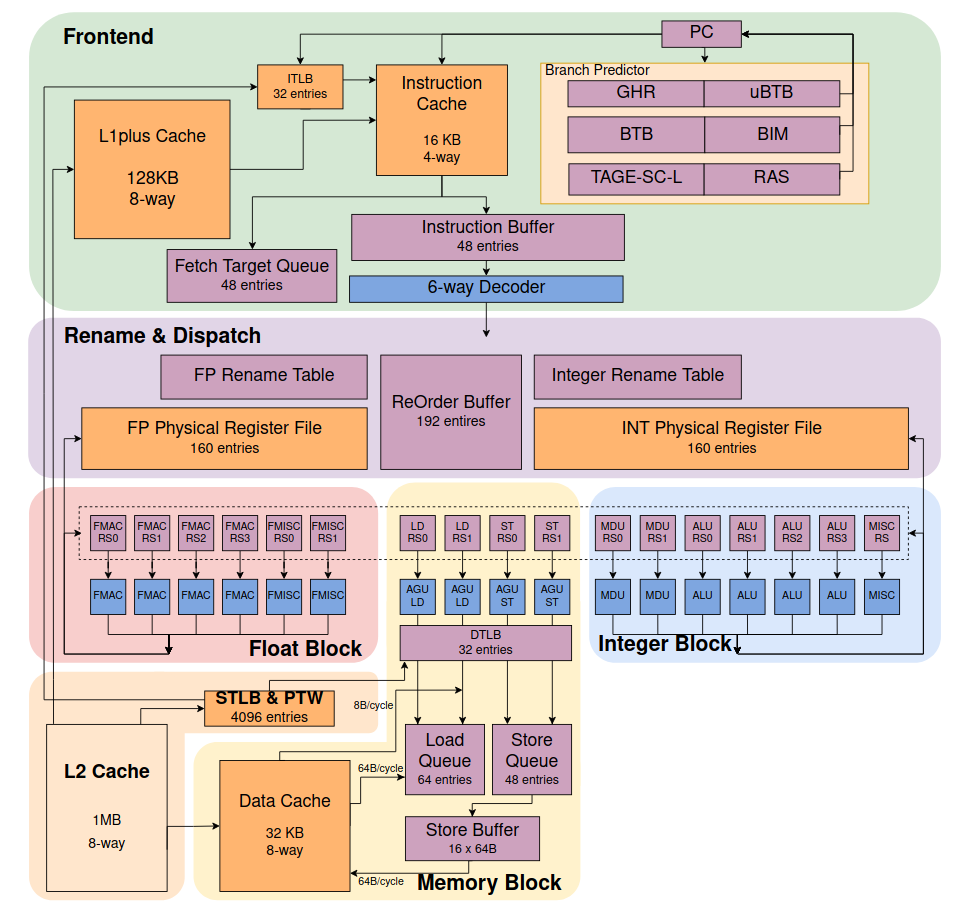

Proiectul a fost publicat sub o descriere a blocurilor hardware în limba daltă, care este tradus în Verilog, o implementare de referință bazată pe FPGA și imagini pentru a simula funcționarea unui cip într-un simulator Verilog deschis.

„Deși obiectivul nostru pe termen lung pe viitor este să fim în conformitate cu [Cortex-] A76, acesta este încă în desfășurare. Avem nevoie de optimizare iterativă practică. Scopul dezvoltării agile nu este depășirea unui colț. Experiența acumulată de Intel și Arm de-a lungul anilor trebuie să o acumulăm încet.

Sunt disponibile și descrieri schematice și arhitecturale (mai mult de 400 de documente și 50 de mii de linii de cod în total), dar cea mai mare parte a documentației este în chineză, plus Debian este folosit ca sistem de operare de referință pentru a testa implementarea FPGA.

XiangShan pretinde a fi cel mai performant cip RISC-V, depășind SiFive P550. Testarea FPGA este programată să fie finalizată luna aceasta și numele de cod „Lacul Yanqi” este un cip prototip cu 8 nuclee care funcționează la 1,3 GHz și este fabricat la TSMC folosind tehnologia de procesare de la 28 nm.

"Sperăm că XiangShan poate supraviețui timp de 30 de ani", a spus Bao, tradus, într-o prezentare recentă a proiectului. „Avem un acord să ne întâlnim din nou peste 30 de ani și apoi să vedem ce va deveni XiangShan. Cu toate acestea, pentru a realiza această dorință, există încă multe probleme și provocări care trebuie rezolvate.

Cipul include o memorie cache de 2 MB, un controler de memorie cu suport pentru memoria DDR4 (până la 32 GB RAM) și o interfață PCIe-3.0-x4.

Performanța primului cip din benchmark-ul SPEC2006 este estimată la 7 / Ghz, ceea ce corespunde cipurilor ARM Cortex-A72 și Cortex-A73.

"Procesul și platforma de proiectare agile pe care le-am construit anterior susțin o echipă de dezvoltare de peste 20 de persoane, ceea ce este departe de a fi suficient", a spus Bao. „Ceea ce trebuie să luăm în considerare acum este cum să construim un set de procese open source standardizate, deschise și deschise, care să poată sprijini dezvoltarea unei comunități open source de 2000 de persoane.”

Până la sfârșitul anului, este planificată producția unui al doilea prototip „South Lake” cu o arhitectură îmbunătățită, care va fi produsă de SMIC cu o tehnologie de proces de 14nm și o creștere a frecvenței la 2 GHz.

Al doilea prototip este de așteptat să obțină o performanță de 10 / Ghz pe benchmark-ul SPEC2006, care este aproape de procesoarele ARM Cortex-A76 și Intel Core i9-10900K și depășește SiFive P550, cel mai rapid procesor RISC-V la 8.65 / Ghz.

În cele din urmă, dacă sunteți interesat să aflați mai multe despre aceasta, puteți consulta codul sursă al XiangShan, care a fost publicat sub MulanPSL2, pe GitHub.

Fuente: https://www.zhihu.com

Sunt extrem de optimiste, chiar dacă este încă testată și dat fiind faptul că cea mai mare parte a documentației este în chineză atunci când au găsit-o în limba engleză. Cu toate acestea, sunt de acord că viitorul va fi RISC-V.