Alguns dias atrás o Instituto de Tecnologia da Informação da Academia Chinesa de Ciências revelou o projeto XiangShan, na qual vem se desenvolvendo desde 2020 um processador aberto de alto desempenho baseado na arquitetura de conjunto de instruções RISC-V (RV64GC) e cujo desempenho se aproxima da velocidade do núcleo Performance P550 mais recente do SiFive.

De acordo com os desenvolvedores, Os núcleos RISC-V subjacentes à CPU Xiangshan se tornarão tão populares entre os designers de processadores como o Linux para sistemas operacionais. O Xiangshan será fabricado com tecnologia de processo de 28 nm pela taiwanesa TSMC (a menos que sanções sejam impostas pelos Estados Unidos) e esta será a primeira geração de núcleos com o codinome Yanqi Lake.

RISC-V fornece um sistema de instrução de máquina aberto e flexível que permite criar microprocessadores para aplicativos arbitrários sem exigir royalties ou impor condições de uso. O RISC-V permite que você crie SoCs e processadores completamente abertos.

Atualmente, com base na especificação RISC-V, várias empresas e comunidades sob várias licenças gratuitas (BSD, MIT, Apache 2.0) estão desenvolvendo várias dezenas de variantes de núcleos de microprocessador já fabricados, SoCs e chips.

Sobre Xiang Shan

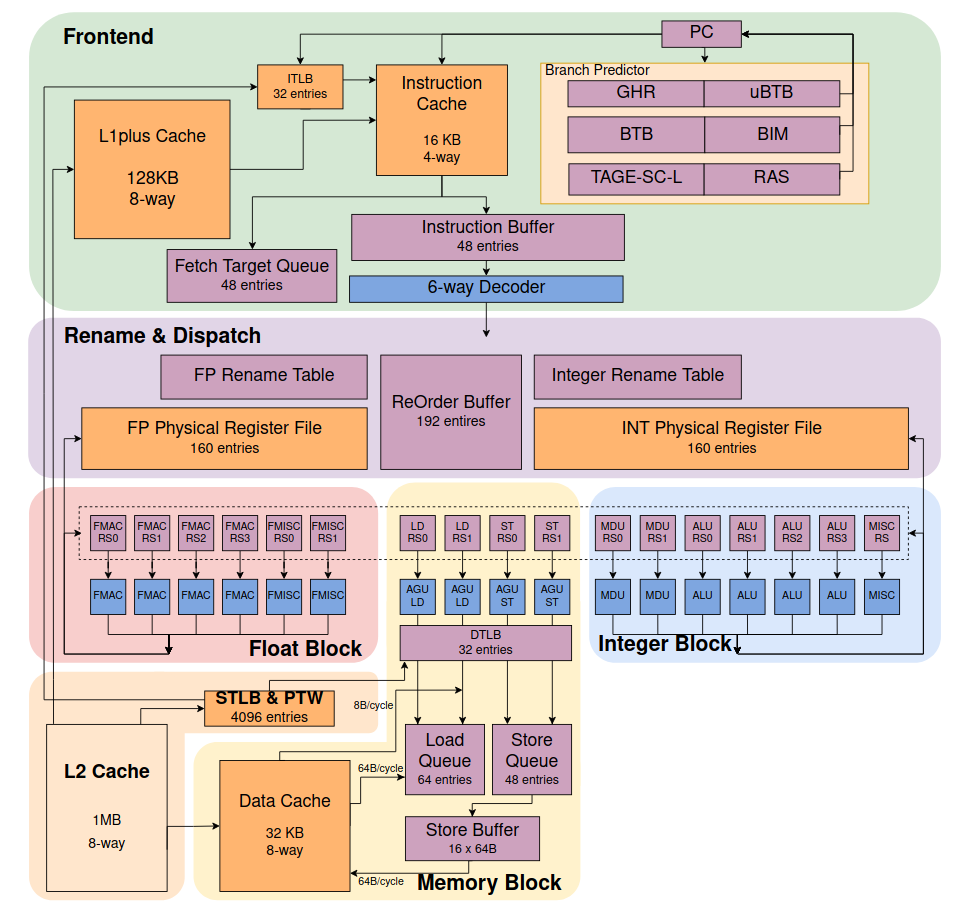

O projeto foi publicado com uma descrição de blocos de hardware na linguagem Chisel, que é traduzido para Verilog, uma implementação de referência baseada em FPGA e imagens para simular a operação de um chip em um simulador Verilog aberto.

“Embora nosso objetivo de longo prazo seja estar em linha com [Cortex-] A76, ele ainda está em andamento. Precisamos de otimização iterativa realista. O objetivo do desenvolvimento ágil não é ultrapassar um canto. A experiência acumulada pela Intel e Arm ao longo dos anos, também temos que acumular lentamente.

Esquemas e descrições de arquitetura também estão disponíveis (mais de 400 documentos e 50 mil linhas de código no total), mas a maior parte da documentação está em chinês, além do Debian ser usado como sistema operacional de referência para testar a implementação do FPGA.

XiangShan afirma ser o chip RISC-V de melhor desempenho, superando o SiFive P550. Os testes FPGA estão programados para serem concluídos este mês e o codinome "Yanqi Lake" é um protótipo de chip de 8 núcleos que opera a 1,3 GHz e é fabricado na TSMC usando tecnologia de processo da 28 nm.

"Temos esperança de que XiangShan possa sobreviver por 30 anos", disse Bao, traduzido, em uma apresentação recente sobre o projeto. “Temos um acordo para nos encontrarmos novamente em 30 anos e, então, ver no que o XiangShan se tornará. No entanto, para realizar esse desejo, ainda existem muitos problemas e desafios que precisam ser resolvidos.

O chip inclui um cache de 2 MB, um controlador de memória com suporte para memória DDR4 (até 32 GB de RAM) e uma interface PCIe-3.0-x4.

O desempenho do primeiro chip no benchmark SPEC2006 é estimado em 7 / Ghz, o que corresponde aos chips ARM Cortex-A72 e Cortex-A73.

"O processo de design ágil e a plataforma que construímos anteriormente dão suporte a uma equipe de desenvolvimento de mais de 20 pessoas, o que está longe de ser suficiente", disse Bao. "O que precisamos considerar agora é como construir um conjunto de processos abertos padronizados e de código aberto que podem apoiar o desenvolvimento de uma comunidade de código aberto de 2000 pessoas."

Até o final do ano, está prevista a produção de um segundo protótipo "South Lake" com arquitetura aprimorada, que será produzida pela SMIC com tecnologia de processo de 14nm e aumento de frequência para 2 GHz.

O segundo protótipo deve atingir um desempenho de 10 / Ghz no benchmark SPEC2006, que está perto dos processadores ARM Cortex-A76 e Intel Core i9-10900K, e supera o SiFive P550, o CPU RISC-V mais rápido com 8.65 / Ghz.

Por fim, se você estiver interessado em saber mais sobre o assunto, pode consultar o código-fonte do XiangShan, que foi publicado sob o MulanPSL2, no GitHub.

fonte: https://www.zhihu.com

Eles estão excessivamente otimistas, embora ainda esteja sendo testado e dado o fato de que a maior parte da documentação está em chinês quando a encontraram em inglês. No entanto, concordo que o futuro será RISC-V.