Paar dagen geleden het Instituut voor Informatietechnologie van de Chinese Academie van Wetenschappen onthuld het project XiangShan, waarin het zich sinds 2020 ontwikkelt; een high-performance open processor gebaseerd op de RISC-V (RV64GC) instructieset-architectuur en waarvan de prestaties de snelheid benaderen van SiFive's nieuwste Performance P550 core.

Volgens de ontwikkelaars RISC-V-kernen die ten grondslag liggen aan Xiangshan CPU zullen zo populair worden onder ontwerpers van processors zoals Linux voor besturingssystemen. Xiangshan zal worden vervaardigd met behulp van een 28nm-procestechnologie door het Taiwanese TSMC (tenzij sancties worden opgelegd door de Verenigde Staten) en dit zal de eerste generatie kernen zijn met de codenaam Yanqi Lake.

RISC-V biedt een open en flexibel machine-instructiesysteem waarmee u microprocessors voor willekeurige toepassingen kunt maken zonder royalty's of gebruiksvoorwaarden op te leggen. Met RISC-V kunt u volledig open SoC's en processors maken.

Momenteel ontwikkelen verschillende bedrijven en gemeenschappen onder verschillende gratis licenties (BSD, MIT, Apache 2.0) op basis van de RISC-V-specificatie enkele tientallen varianten van reeds vervaardigde microprocessorkernen, SoC's en chips.

Over XiangShan

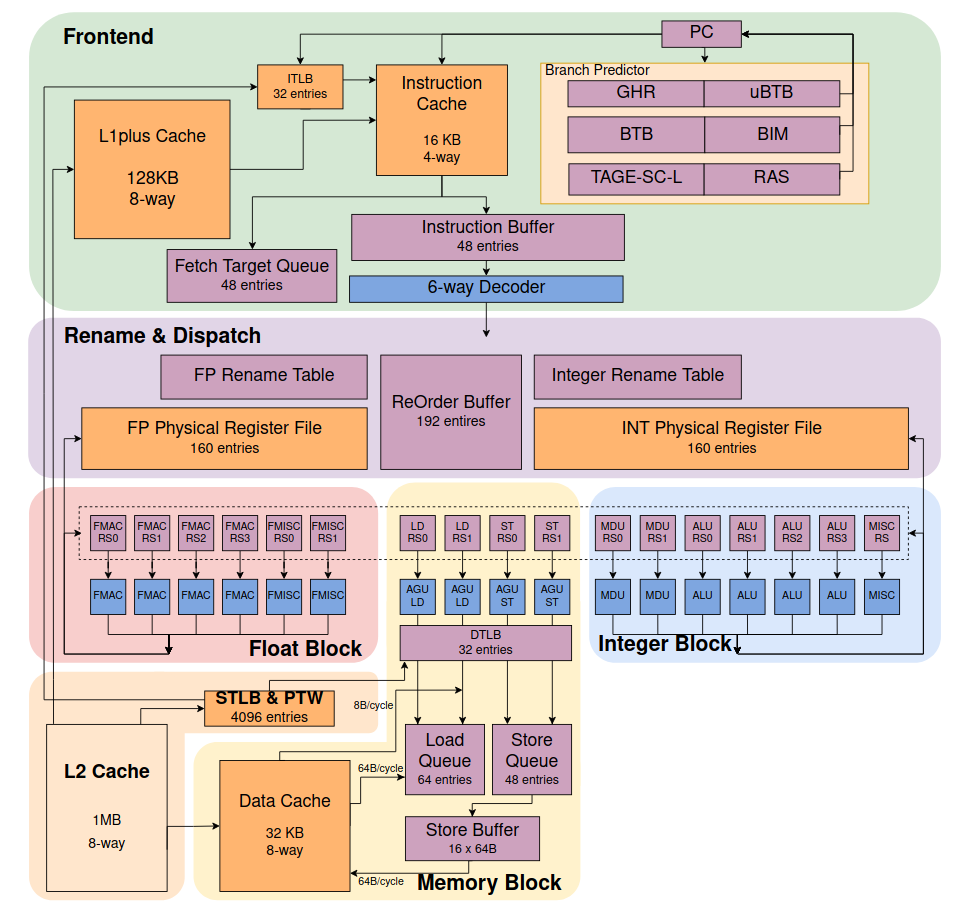

El proyecto is gepubliceerd onder een beschrijving van hardwareblokken in de beiteltaal, die wordt vertaald naar Verilog, een referentie-implementatie op basis van FPGA en afbeeldingen om de werking van een chip in een open Verilog-simulator te simuleren.

"Hoewel ons langetermijndoel voor de toekomst is om in lijn te zijn met [Cortex-] A76, is het nog steeds in uitvoering. We hebben nuchtere iteratieve optimalisatie nodig. Het doel van agile ontwikkelen is niet om een bocht in te halen. De ervaring die Intel en Arm in de loop der jaren hebben opgedaan, moeten we ook langzaam opbouwen.

Schema's en architectuurbeschrijvingen zijn ook beschikbaar (meer dan 400 documenten en 50 duizend regels code in totaal), maar de meeste documentatie is in het Chinees, en Debian wordt gebruikt als referentiebesturingssysteem om de FPGA-implementatie te testen.

XiangShan beweert de best presterende RISC-V-chip te zijn en presteert beter dan de SiFive P550. FPGA-tests zijn gepland voor deze maand en de codenaam "Yanqi Lake" is een 8-core prototype-chip die werkt op 1,3 GHz en wordt vervaardigd bij TSMC met behulp van procestechnologie van 28 nm.

"We hebben goede hoop dat XiangShan 30 jaar kan overleven", zei Bao in een recente presentatie over het project. “We hebben afgesproken om elkaar over 30 jaar weer te ontmoeten en dan te zien wat XiangShan zal worden. Om deze wens te realiseren, zijn er echter nog veel problemen en uitdagingen die moeten worden opgelost.

De chip bevat een cache van 2 MB, een geheugencontroller met ondersteuning voor DDR4-geheugen (tot 32 GB RAM) en een PCIe-3.0-x4-interface.

De prestaties van de eerste chip in de SPEC2006-benchmark worden geschat op 7 / Ghz, wat overeenkomt met de ARM Cortex-A72- en Cortex-A73-chips.

"Het agile ontwerpproces en platform dat we eerder hebben gebouwd, ondersteunen een ontwikkelteam van meer dan 20 mensen, wat verre van voldoende is", zegt Bao. "Wat we nu moeten overwegen, is hoe we een reeks gestandaardiseerde, open en open source open processen kunnen bouwen die de ontwikkeling van een open source-gemeenschap van 2000 mensen kunnen ondersteunen."

De productie van een tweede prototype is gepland voor het einde van het jaar "South Lake" met een verbeterde architectuur, die door SMIC zal worden geproduceerd met een procestechnologie van 14nm en een frequentieverhoging naar 2 GHz.

Het tweede prototype zal naar verwachting een prestatie van 10 / Ghz . behalen op de SPEC2006-benchmark, die dicht bij de ARM Cortex-A76- en Intel Core i9-10900K-processors ligt, en beter presteert dan de SiFive P550, de snelste RISC-V-CPU met 8.65 / Ghz.

Tot slot, als u er meer over wilt weten, kunt u de broncode van XiangShan raadplegen, die is gepubliceerd onder de MulanPSL2, op GitHub.

bron: https://www.zhihu.com

Ze zijn te optimistisch, ook al wordt het nog steeds getest en gezien het feit dat de meeste documentatie in het Chinees was toen ze het in het Engels vonden. Ik ben het er echter mee eens dat de toekomst RISC-V zal zijn.