Beberapa hari yang lalu Institut Teknologi Maklumat Akademi Sains China dilancarkan projek itu XiangShan, di mana ia telah berkembang sejak tahun 2020 pemproses terbuka berprestasi tinggi berdasarkan seni bina set arahan RISC-V (RV64GC) dan yang prestasinya mendekati kelajuan teras Performance P550 terbaru SiFive.

Menurut pemaju, Inti RISC-V yang mendasari CPU Xiangshan akan menjadi begitu popular antara pereka bentuk pemproses seperti Linux untuk sistem operasi. Xiangshan akan dihasilkan menggunakan teknologi proses 28nm oleh TSMC Taiwan (kecuali jika sekatan dikenakan oleh Amerika Syarikat) dan ini akan menjadi generasi pertama teras yang diberi nama Yanqi Lake.

RISC-V menyediakan sistem arahan mesin yang terbuka dan fleksibel yang membolehkan anda membuat mikropemproses untuk aplikasi sewenang-wenangnya tanpa memerlukan royalti atau mengenakan syarat penggunaan. RISC-V membolehkan anda membuat SoC dan pemproses yang terbuka sepenuhnya.

Pada masa ini, berdasarkan spesifikasi RISC-V, beberapa syarikat dan komuniti di bawah pelbagai lesen percuma (BSD, MIT, Apache 2.0) sedang mengembangkan beberapa lusin varian teras mikropemproses, SoC dan cip yang sudah dihasilkan.

Mengenai XiangShan

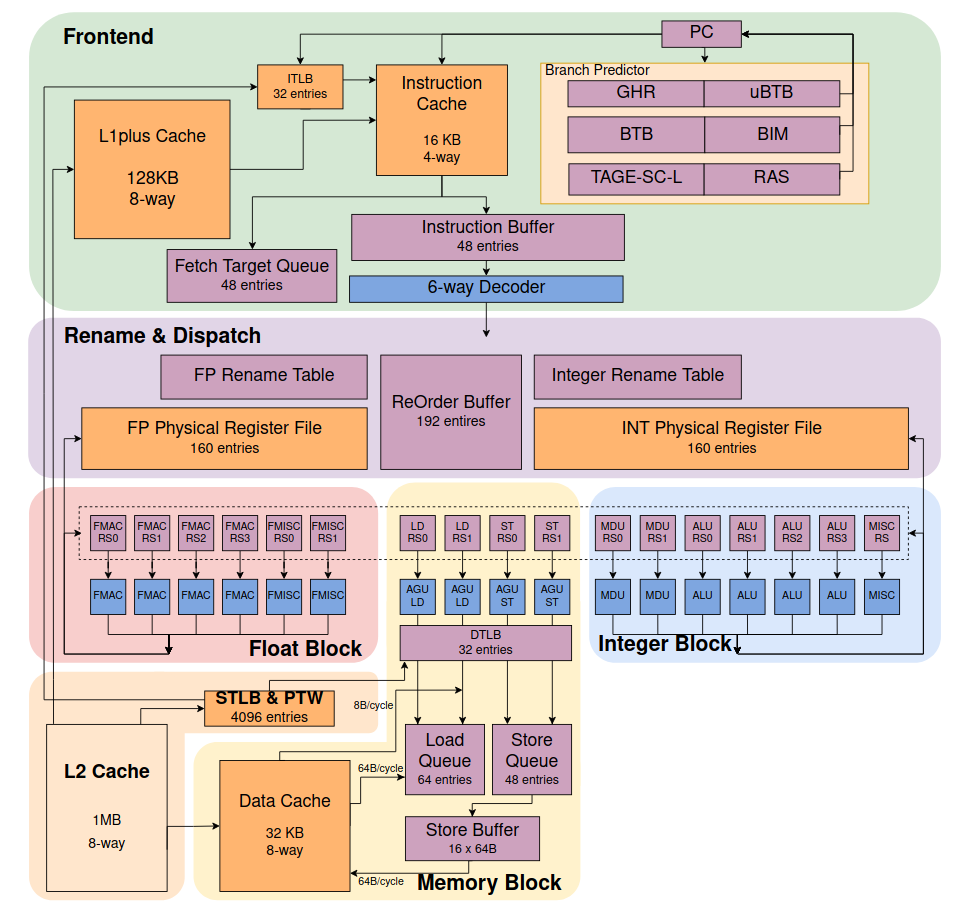

Projek itu telah diterbitkan di bawah penerangan mengenai blok perkakasan dalam bahasa Pahat, yang diterjemahkan ke dalam Verilog, implementasi rujukan berdasarkan FPGA dan gambar untuk mensimulasikan operasi cip di simulator Verilog terbuka.

"Walaupun tujuan jangka panjang kita maju adalah sejajar dengan [Cortex-] A76, ia masih berjalan. Kami memerlukan pengoptimuman berulang dari bawah ke bumi. Tujuan pembangunan tangkas bukan untuk mengatasi sudut. Pengalaman yang dikumpulkan oleh Intel dan Arm selama bertahun-tahun, kami juga harus mengumpulkan secara perlahan.

Skema dan deskripsi seni bina juga ada (lebih dari 400 dokumen dan 50 ribu baris kod secara keseluruhan), tetapi kebanyakan dokumentasi dalam bahasa Cina, ditambah Debian digunakan sebagai sistem operasi rujukan untuk menguji pelaksanaan FPGA.

XiangShan mengaku sebagai cip RISC-V dengan prestasi tertinggi, mengungguli SiFive P550. Ujian FPGA dijadualkan selesai bulan ini dan nama kod "Yanqi Lake" adalah cip prototaip 8 teras yang beroperasi pada 1,3 GHz dan dihasilkan di TSMC menggunakan teknologi proses dari 28 nm.

"Kami berharap XiangShan dapat bertahan selama 30 tahun," kata Bao, yang diterjemahkan, dalam pembentangan mengenai projek tersebut baru-baru ini. "Kami mempunyai perjanjian untuk bertemu lagi dalam 30 tahun dan kemudian melihat apa yang akan menjadi XiangShan. Namun, untuk merealisasikan hasrat ini, masih banyak masalah dan cabaran yang perlu diselesaikan.

Cip merangkumi cache 2MB, pengawal memori dengan sokongan untuk memori DDR4 (RAM hingga 32 GB) dan antara muka PCIe-3.0-x4.

Prestasi cip pertama dalam penanda aras SPEC2006 dianggarkan pada 7 / Ghz, yang sepadan dengan cip ARM Cortex-A72 dan Cortex-A73.

"Proses dan platform reka bentuk lincah yang kami bina sebelumnya menyokong pasukan pembangunan lebih dari 20 orang, yang jauh dari cukup," kata Bao. "Apa yang perlu kita pertimbangkan sekarang adalah bagaimana membangun sekumpulan proses terbuka sumber terbuka, standard dan terbuka yang dapat mendukung pengembangan komuniti sumber terbuka yang terdiri dari 2000 orang."

Menjelang akhir tahun, pengeluaran prototaip kedua dirancang "South Lake" dengan seni bina yang lebih baik, yang akan dihasilkan oleh SMIC dengan teknologi proses 14nm dan peningkatan frekuensi menjadi 2 GHz.

Prototaip kedua dijangka mencapai prestasi 10 / Ghz pada penanda aras SPEC2006, yang hampir dengan pemproses ARM Cortex-A76 dan Intel Core i9-10900K, dan mengungguli SiFive P550, CPU RISC-V terpantas pada 8.65 / Ghz.

Akhirnya, jika anda berminat untuk mengetahui lebih lanjut mengenainya, anda boleh merujuk kod sumber XiangShan, yang telah diterbitkan di bawah MulanPSL2, di GitHub.

Fuente: https://www.zhihu.com

Mereka terlalu optimis walaupun masih diuji dan mengingat fakta bahawa kebanyakan dokumentasi berbahasa Cina ketika mereka menemukannya dalam bahasa Inggeris. Walau bagaimanapun, saya bersetuju bahawa masa depan adalah RISC-V.