Pirms dažām dienām atklāja Ķīnas Zinātņu akadēmijas Informācijas tehnoloģiju institūtu projektu XiangShan, kurā tā attīstās kopš 2020. gada augstas veiktspējas atvērts procesors, kas balstīts uz RISC-V (RV64GC) instrukciju komplekta arhitektūru un kura veiktspēja tuvojas SiFive jaunākā Performance P550 kodola ātrumam.

Pēc izstrādātāju domām, Xiangshan CPU pamatā esošie RISC-V kodoli kļūs tik populāri starp tādu procesoru dizaineriem kā Linux operētājsistēmām. Sjaņshanu ražos, izmantojot Taivānas TSMC, izmantojot 28 nm procesoru tehnoloģiju (ja vien Amerikas Savienotās Valstis neieviesīs sankcijas), un šī būs pirmās kodolu paaudze, kuras kods ir Yanqi Lake.

RISC-V nodrošina atvērtu un elastīgu mašīnu instrukciju sistēmu kas ļauj jums izveidot mikroprocesorus patvaļīgām lietojumprogrammām, neprasot honorārus vai neuzliekot lietošanas nosacījumus. RISC-V ļauj jums izveidot pilnīgi atvērtus SoC un procesorus.

Pašlaik, pamatojoties uz RISC-V specifikāciju, vairāki uzņēmumi un kopienas ar dažādām bezmaksas licencēm (BSD, MIT, Apache 2.0) izstrādā vairākus desmitus jau ražotu mikroprocesoru kodolu, SoC un mikroshēmu variantu.

Par Sjanshanu

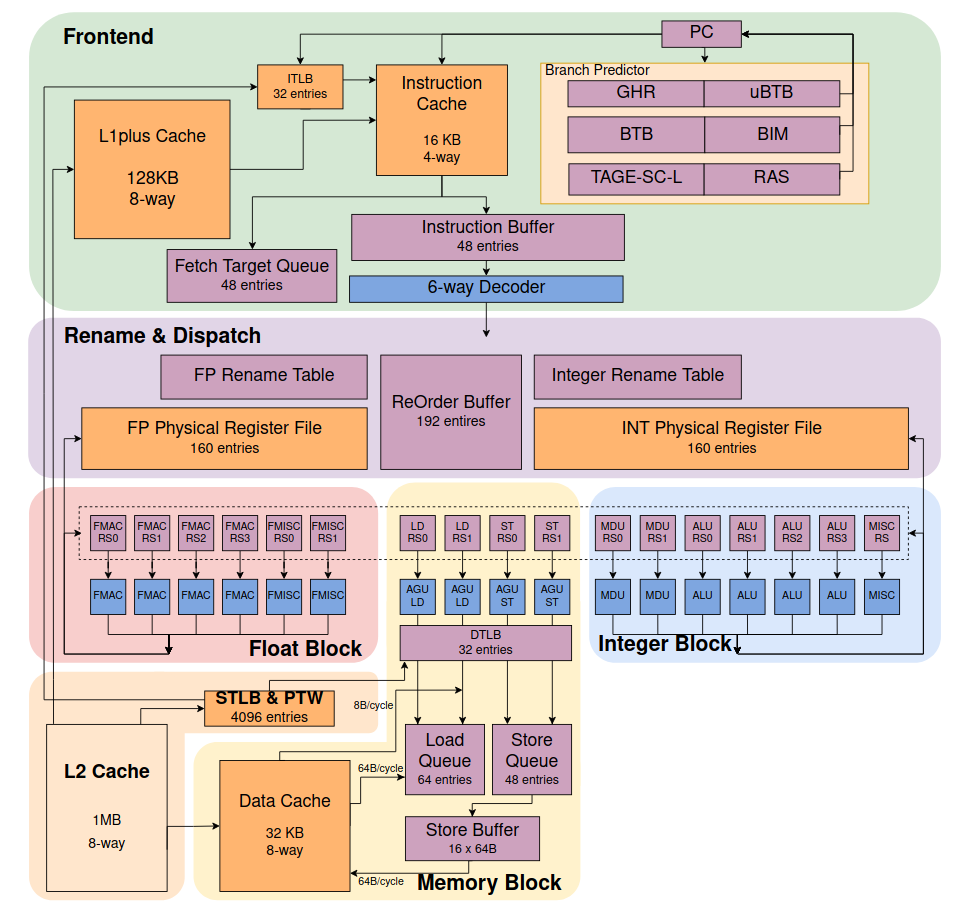

Projekts ir publicēts aparatūras bloku aprakstā kaltu valodā, kas tiek tulkots Verilog, atsauces ieviešana, kuras pamatā ir FPGA un attēli, lai simulētu mikroshēmas darbību atvērtā Verilog simulatorā.

Lai gan mūsu ilgtermiņa mērķis ir būt saskaņā ar [Cortex-] A76, tas joprojām tiek turpināts. Mums nepieciešama piezemēta iteratīva optimizācija. Veiklas attīstības mērķis nav apsteigt stūri. Pieredze, ko Intel un Arm ir uzkrājuši gadu gaitā, mums arī ir jākrāj lēni.

Pieejamas arī shēmas un arhitektūras apraksti (kopā vairāk nekā 400 dokumentu un 50 tūkstoši koda rindiņu), bet lielākā daļa dokumentācijas ir ķīniešu valodā, kā arī Debian tiek izmantota kā atsauces operētājsistēma, lai pārbaudītu FPGA ieviešanu.

XiangShan apgalvo, ka ir RISC-V mikroshēma ar vislabāko veiktspēju, pārspējot SiFive P550. FPGA testus plānots pabeigt šomēnes un koda nosaukums "Yanqi Lake" ir 8 kodolu prototipa mikroshēma, kas darbojas 1,3 GHz frekvencē un tiek ražots TSMC, izmantojot procesu tehnoloģiju no 28 nm.

"Mēs ceram, ka XiangShan var izdzīvot 30 gadus," nesenā projekta prezentācijā teica Bao tulkojumā. "Mums ir vienošanās atkal tikties pēc 30 gadiem un tad redzēt, kas kļūs par Sjanshanu. Tomēr, lai realizētu šo vēlmi, joprojām ir jāatrisina daudzas problēmas un izaicinājumi.

Mikroshēma ietver 2 MB kešatmiņu, atmiņas kontrolieris ar atbalsts DDR4 atmiņai (līdz 32 GB RAM) un PCIe-3.0-x4 interfeiss.

Pirmās mikroshēmas veiktspēja SPEC2006 etalonā tiek lēsta 7 / Ghz, kas atbilst ARM Cortex-A72 un Cortex-A73 mikroshēmām.

"Iepriekš izveidotais veiklais projektēšanas process un platforma atbalsta vairāk nekā 20 cilvēku lielu attīstības komandu, kas nebūt nav pietiekami," sacīja Bao. "Mums tagad jāapsver, kā izveidot standartizētu, atvērtu un atvērtu pirmkodu atvērtu procesu kopumu, kas var atbalstīt 2000 cilvēku atvērta pirmkoda kopienas attīstību."

Līdz gada beigām ir plānots izgatavot otru prototipu "Dienvidu ezers" ar uzlabotu arhitektūru, ko ražos SMIC ar procesa tehnoloģiju 14 nm un frekvences palielināšanu līdz 2 GHz.

Paredzams, ka otrais prototips sasniegs 10 / Ghz veiktspēju uz SPEC2006 etalona, kas ir tuvu ARM Cortex-A76 un Intel Core i9-10900K procesoriem, un pārspēj SiFive P550, ātrāko RISC-V procesoru ar ātrumu 8.65 / Ghz.

Visbeidzot, ja vēlaties uzzināt vairāk par to, varat iepazīties ar XiangShan avota kodu, kas ir publicēts zem MulanPSL2, vietnē GitHub.

Fuente: https://www.zhihu.com

Viņi ir pārāk optimistiski, kaut arī to joprojām pārbauda, ņemot vērā faktu, ka lielākā daļa dokumentācijas ir ķīniešu valodā, kad viņi to atrada angļu valodā. Tomēr es piekrītu, ka nākotne būs RISC-V.