לפני כמה ימים המכון לטכנולוגיית המידע של האקדמיה הסינית למדעים שנחשף את הפרויקט שיאנגשאן, בה היא מתפתחת מאז שנת 2020 מעבד פתוח בעל ביצועים גבוהים המבוסס על ארכיטקטורת ערכת ההוראות של RISC-V (RV64GC) וביצועיו מתקרבים למהירות ליבת ה- Performance P550 האחרונה של SiFive.

לדברי היזמים, ליבות RISC-V העומדות בבסיס מעבד Xiangshan יהפכו לפופולריות כל כך בקרב מעצבי מעבדים כמו לינוקס למערכות הפעלה. שיאנגשאן תייצר בטכנולוגיית תהליכים של 28 ננומטר על ידי TSMC הטייוואנית (אלא אם כן יוטלו סנקציות על ידי ארצות הברית) וזה יהיה הדור הראשון של ליבות עם קוד הקודם אגם ינקי.

RISC-V מספקת מערכת הוראות מכונה פתוחה וגמישה המאפשר ליצור מיקרו-מעבדים ליישומים שרירותיים מבלי לדרוש תמלוגים או הטלת תנאי שימוש. RISC-V מאפשר לך ליצור SoCs ומעבדים פתוחים לחלוטין.

נכון לעכשיו, בהתבסס על מפרט RISC-V, כמה חברות וקהילות תחת רישיונות חינמיים שונים (BSD, MIT, Apache 2.0) מפתחות כמה עשרות גרסאות של ליבות מיקרו-מעבדים שכבר יוצרו, SoCs וצ'יפס.

על שיאנגשאן

proyecto אל פורסם בתיאור של חסימות חומרה בשפת האזיזל, שמתורגם ל- Verilog, יישום הפניה המבוסס על FPGA ותמונות כדי לדמות את פעולת השבב בסימולטור Verilog פתוח.

"למרות שהמטרה ארוכת הטווח שלנו בהמשך היא להיות בקו אחד עם [Cortex-] A76, היא עדיין בעיצומה. אנו זקוקים לאופטימיזציה איטרטיבית מהארץ. מטרת הפיתוח הזריז אינה לעקוף פינה. הניסיון שנצבר על ידי אינטל וארם לאורך השנים, אנחנו גם צריכים להצטבר לאט.

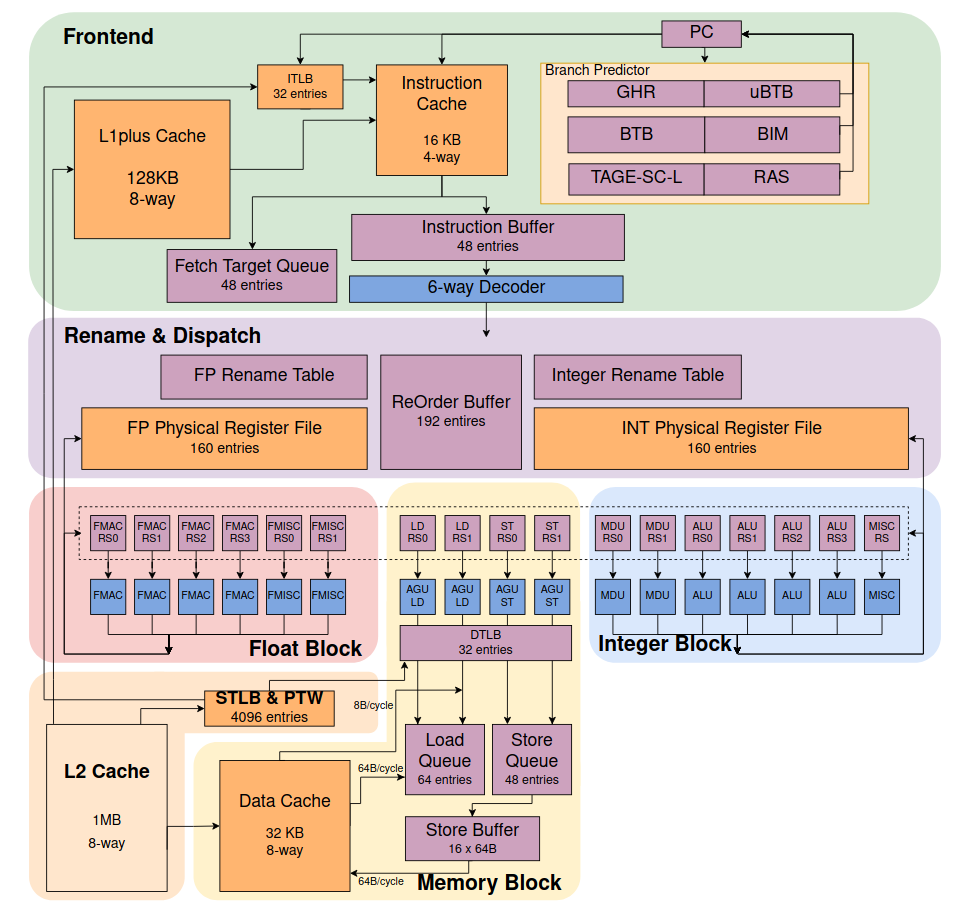

ניתן להשיג גם תיאור סכמטי וארכיטקטורה (יותר מ -400 מסמכים ו -50 אלף שורות קוד בסך הכל), אך מרבית התיעוד הוא בסינית, בנוסף דביאן משמשת כמערכת הפעלה הפניה לבדיקת יישום ה- FPGA.

XiangShan טוען שהוא שבב ה- RISC-V בעל הביצועים הגבוהים ביותר, בהשוואה ל SiFive P550. בדיקות FPGA אמורות להסתיים החודש ושם הקוד "אגם יאנקי" הוא שבב אב-טיפוס בעל 8 ליבות הפועל במהירות 1,3 ג'יגה הרץ ומיוצר ב- TSMC באמצעות טכנולוגיית תהליכים מ- 28 ננומטר.

"אנו מקווים כי שיאנגשאן תוכל לשרוד במשך 30 שנה," אמר באו, שתורגם, במצגת שנערכה לאחרונה על הפרויקט. "יש לנו הסכם להיפגש שוב בעוד 30 שנה ואז לראות מה יהפוך שיאנגשאן. עם זאת, כדי לממש משאלה זו, ישנם עדיין בעיות ואתגרים רבים שיש לפתור.

השבב כולל מטמון של 2 מגה-בתים, בקר זיכרון עם תמיכה בזיכרון DDR4 (עד 32 GB של זיכרון RAM) וממשק PCIe-3.0-x4.

הביצועים של השבב הראשון במבחן ה- SPEC2006 נאמדים בכ- 7 / Ghz, התואמים לשבבי ARM Cortex-A72 ו- Cortex-A73.

"תהליך העיצוב והפלטפורמה הזריזים שבנו תומכים בעבר בצוות פיתוח של יותר מ -20 אנשים, וזה רחוק מלהיות מספיק", אמר באו. "מה שעלינו לשקול כעת הוא כיצד לבנות סט של תהליכים פתוחים בקוד פתוח ופתוח בקוד פתוח שיכולים לתמוך בפיתוח קהילת קוד פתוח המונה 2000 איש."

הפקה של אב טיפוס שני מתוכננת לסוף השנה "South Lake" עם ארכיטקטורה משופרת, שתופק על ידי SMIC בטכנולוגיית תהליכים של 14nm ותוספת תדרים ל -2 GHz.

האב-טיפוס השני צפוי להשיג ביצועים של 10 / Ghz על מדד ה- SPEC2006, הקרוב למעבדי ARM Cortex-A76 ו- Intel Core i9-10900K, ומעלה על SiFive P550, מעבד ה- RISC-V המהיר ביותר ב -8.65 / Ghz.

לבסוף, אם אתה מעוניין לדעת יותר על כך, תוכל להתייעץ עם קוד המקור של XiangShan, שפורסם תחת MulanPSL2, ב- GitHub.

מקור: https://www.zhihu.com

הם אופטימיים מדי למרות שהוא עדיין נבדק ובהתחשב בעובדה שרוב התיעוד הוא בסינית כשמצאו אותו באנגלית. עם זאת, אני מסכים שהעתיד יהיה RISC-V.