Pochi giorni fa svelato l'Istituto di tecnologia dell'informazione dell'Accademia cinese delle scienze il progetto XiangShan, in cui si sviluppa dal 2020 un processore aperto ad alte prestazioni basato sull'architettura del set di istruzioni RISC-V (RV64GC) e le cui prestazioni si avvicinano alla velocità dell'ultimo core Performance P550 di SiFive.

Secondo gli sviluppatori, I core RISC-V alla base della CPU Xiangshan diventeranno così popolari tra i progettisti di processori come Linux per sistemi operativi. Xiangshan sarà prodotto utilizzando una tecnologia di processo a 28 nm dalla taiwanese TSMC (a meno che non vengano imposte sanzioni dagli Stati Uniti) e questa sarà la prima generazione di core nome in codice Yanqi Lake.

RISC-V fornisce un sistema di istruzione della macchina aperto e flessibile che consente di creare microprocessori per applicazioni arbitrarie senza richiedere royalties o imporre condizioni di utilizzo. RISC-V ti consente di creare SoC e processori completamente aperti.

Attualmente, in base alla specifica RISC-V, diverse aziende e comunità con varie licenze gratuite (BSD, MIT, Apache 2.0) stanno sviluppando diverse dozzine di varianti di core, SoC e chip di microprocessori già prodotti.

A proposito di XiangShan

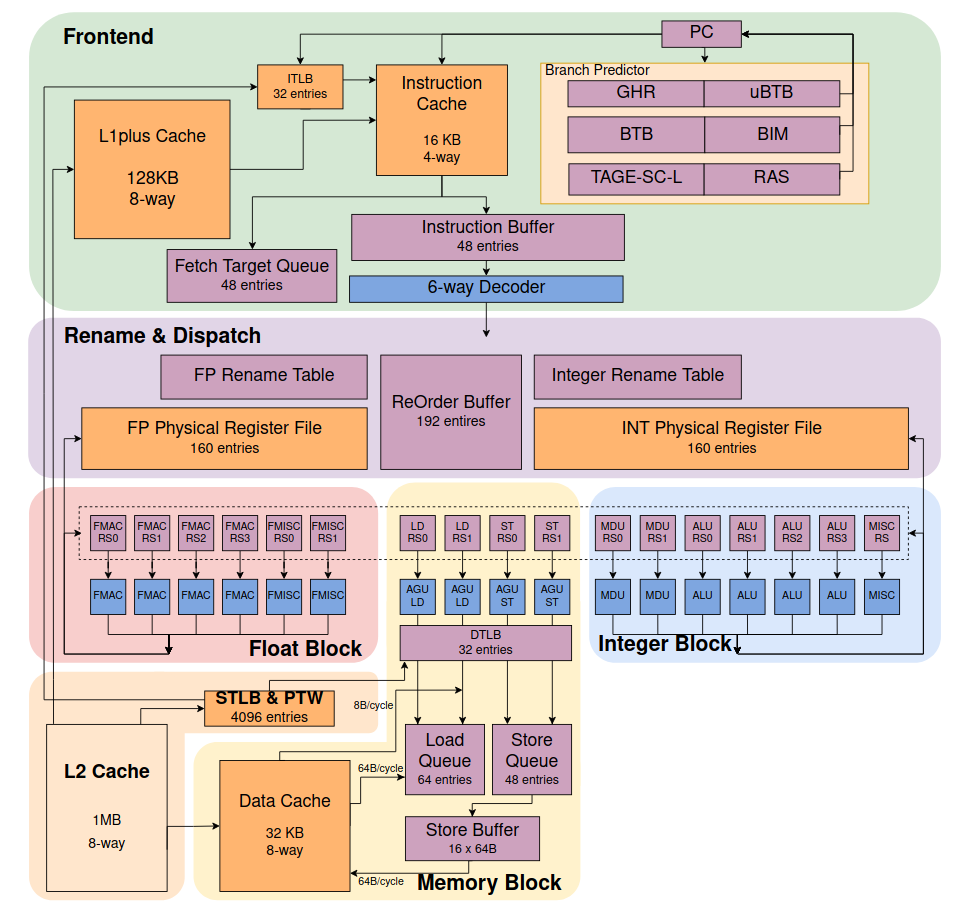

El proyecto è stato pubblicato sotto una descrizione dei blocchi hardware nel linguaggio Chisel, che viene tradotto in Verilog, un'implementazione di riferimento basata su FPGA e immagini per simulare il funzionamento di un chip in un simulatore Verilog aperto.

“Sebbene il nostro obiettivo a lungo termine per il futuro sia essere in linea con [Cortex-] A76, è ancora in corso. Abbiamo bisogno di un'ottimizzazione iterativa concreta. Lo scopo dello sviluppo agile non è superare una curva. L'esperienza accumulata da Intel e Arm nel corso degli anni, dobbiamo anche accumularla lentamente.

Sono disponibili anche schemi e descrizioni dell'architettura (più di 400 documenti e 50mila righe di codice in totale), ma la maggior parte della documentazione è in cinese, inoltre Debian viene utilizzato come sistema operativo di riferimento per testare l'implementazione dell'FPGA.

XiangShan afferma di essere il chip RISC-V più performante, superando il SiFive P550. I test FPGA dovrebbero essere completati questo mese e il nome in codice "Yanqi Lake" è un prototipo di chip a 8 core che opera a 1,3 GHz ed è prodotto presso TSMC utilizzando la tecnologia di processo di 28 nm.

"Speriamo che XiangShan possa sopravvivere per 30 anni", ha detto Bao, tradotto, in una recente presentazione del progetto. “Abbiamo un accordo per incontrarci di nuovo tra 30 anni e poi vedere cosa diventerà XiangShan. Tuttavia, per realizzare questo desiderio, ci sono ancora molti problemi e sfide che devono essere risolti.

Il chip include una cache da 2 MB, un controller di memoria con supporto per la memoria DDR4 (fino a 32 GB di RAM) e un'interfaccia PCIe-3.0-x4.

Le prestazioni del primo chip nel benchmark SPEC2006 sono stimate a 7/Ghz, che corrisponde ai chip ARM Cortex-A72 e Cortex-A73.

"Il processo di progettazione agile e la piattaforma che abbiamo creato in precedenza supportano un team di sviluppo di oltre 20 persone, il che è tutt'altro che sufficiente", ha affermato Bao. "Quello che dobbiamo considerare ora è come costruire una serie di processi standard, open source e open source in grado di supportare lo sviluppo di una comunità open source di 2000 persone".

Entro fine anno è prevista la produzione di un secondo prototipo "South Lake" con un'architettura migliorata, che sarà prodotta da SMIC con una tecnologia di processo di 14 nm e un aumento di frequenza a 2 GHz.

Il secondo prototipo dovrebbe raggiungere una performance di 10/Ghz sul benchmark SPEC2006, che è vicino ai processori ARM Cortex-A76 e Intel Core i9-10900K, e supera il SiFive P550, la CPU RISC-V più veloce a 8.65 / Ghz.

Infine, se sei interessato a saperne di più, puoi consultare il codice sorgente di XiangShan, che è stato pubblicato sotto il MulanPSL2, su GitHub.

fonte: https://www.zhihu.com

Sono eccessivamente ottimisti anche se è ancora in fase di test e dato che la maggior parte della documentazione è in cinese quando l'hanno trovata in inglese. Tuttavia, sono d'accordo che il futuro sarà RISC-V.