Beberapa hari yang lalu Institut Teknologi Informasi Akademi Ilmu Pengetahuan China diresmikan proyek XiangShan, yang telah berkembang sejak 2020 prosesor terbuka berkinerja tinggi berdasarkan arsitektur set instruksi RISC-V (RV64GC) dan yang kinerjanya mendekati kecepatan inti Performance P550 terbaru SiFive.

Menurut pengembangnya, Inti RISC-V yang mendasari CPU Xiangshan akan menjadi sangat populer di antara para perancang prosesor seperti Linux untuk sistem operasi. Xiangshan akan diproduksi menggunakan teknologi proses 28nm oleh TSMC Taiwan (kecuali sanksi dijatuhkan oleh Amerika Serikat) dan ini akan menjadi inti generasi pertama dengan nama sandi Danau Yanqi.

RISC-V menyediakan sistem instruksi mesin yang terbuka dan fleksibel yang memungkinkan Anda membuat mikroprosesor untuk aplikasi sewenang-wenang tanpa memerlukan royalti atau ketentuan penggunaan yang memaksakan. RISC-V memungkinkan Anda membuat SoC dan prosesor yang sepenuhnya terbuka.

Saat ini, berdasarkan spesifikasi RISC-V, beberapa perusahaan dan komunitas di bawah berbagai lisensi gratis (BSD, MIT, Apache 2.0) sedang mengembangkan beberapa lusin varian inti mikroprosesor, SoC, dan chip yang sudah diproduksi.

Tentang XiangShan

Proyek telah diterbitkan di bawah deskripsi blok perangkat keras dalam bahasa Pahat, yang diterjemahkan ke dalam Verilog, implementasi referensi berdasarkan FPGA dan gambar untuk mensimulasikan pengoperasian chip dalam simulator Verilog terbuka.

“Meskipun tujuan jangka panjang kami ke depan adalah sejalan dengan [Cortex-] A76, itu masih dalam proses. Kami membutuhkan optimasi iteratif yang membumi. Tujuan dari pengembangan tangkas bukanlah untuk menyalip tikungan. Pengalaman yang diakumulasikan oleh Intel dan Arm selama bertahun-tahun, juga harus kita akumulasi secara perlahan.

Skema dan deskripsi arsitektur juga tersedia (total lebih dari 400 dokumen dan 50 ribu baris kode), tetapi sebagian besar dokumentasi dalam bahasa Cina, ditambah Debian digunakan sebagai sistem operasi referensi untuk menguji implementasi FPGA.

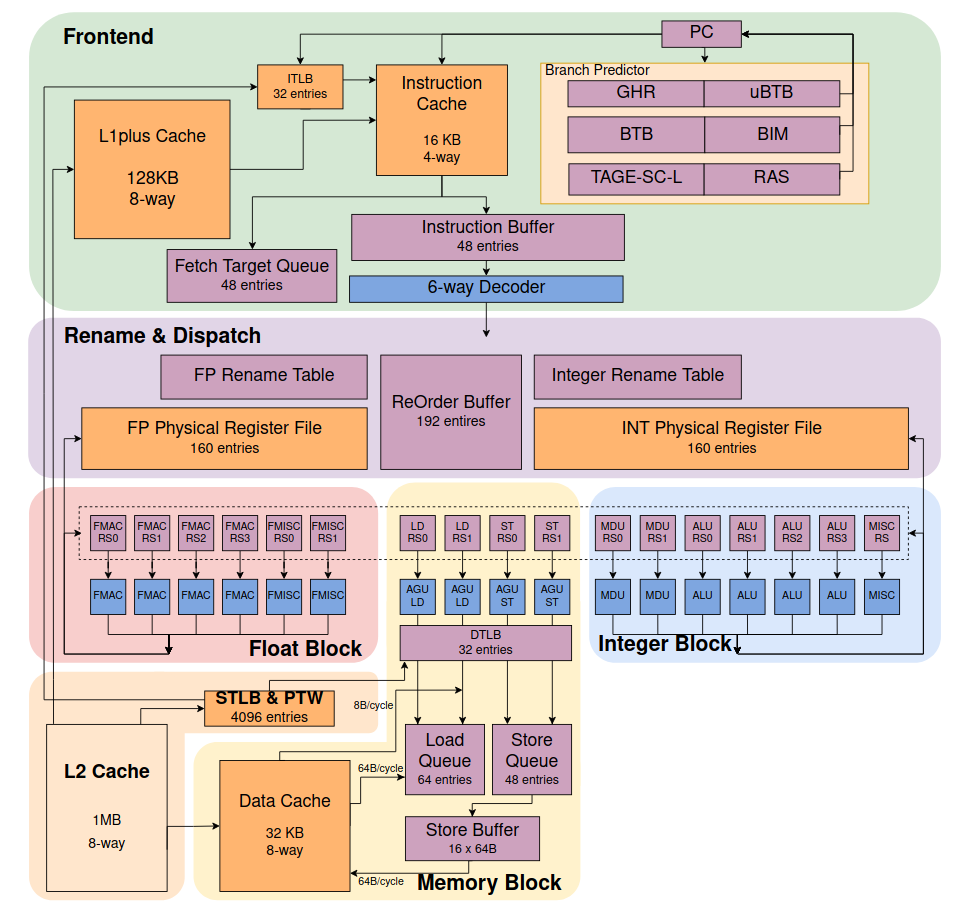

XiangShan mengklaim sebagai chip RISC-V berperforma tertinggi, mengungguli SiFive P550. Pengujian FPGA dijadwalkan akan selesai bulan ini dan nama kodenya "Yanqi Lake" adalah chip prototipe 8-inti yang beroperasi pada 1,3 GHz dan diproduksi di TSMC menggunakan teknologi proses dari 28 nm.

"Kami berharap XiangShan dapat bertahan selama 30 tahun," kata Bao, dalam presentasinya baru-baru ini tentang proyek tersebut. “Kami memiliki kesepakatan untuk bertemu lagi dalam 30 tahun dan kemudian melihat apa yang akan menjadi XiangShan. Namun, untuk mewujudkan keinginan tersebut, masih banyak masalah dan tantangan yang harus diselesaikan.

Chip termasuk cache 2MB, pengontrol memori dengan dukungan untuk memori DDR4 (hingga 32 GB RAM) dan antarmuka PCIe-3.0-x4.

Kinerja chip pertama di benchmark SPEC2006 diperkirakan 7 / Ghz, yang sesuai dengan chip ARM Cortex-A72 dan Cortex-A73.

"Proses desain dan platform tangkas yang kami bangun sebelumnya mendukung tim pengembangan lebih dari 20 orang, yang jauh dari cukup," kata Bao. "Yang perlu kita pertimbangkan sekarang adalah bagaimana membangun serangkaian proses open source yang terstandarisasi, terbuka, dan open source yang dapat mendukung pengembangan komunitas open source yang terdiri dari 2000 orang."

Pada akhir tahun, produksi prototipe kedua direncanakan "South Lake" dengan arsitektur yang ditingkatkan, akan diproduksi oleh SMIC dengan teknologi proses 14nm dan peningkatan frekuensi hingga 2 GHz.

Prototipe kedua diharapkan mencapai kinerja 10 / Ghz pada benchmark SPEC2006, yang mendekati prosesor ARM Cortex-A76 dan Intel Core i9-10900K, dan mengungguli SiFive P550, CPU RISC-V tercepat pada 8.65 / Ghz.

Akhirnya, jika Anda tertarik untuk mengetahui lebih banyak tentangnya, Anda dapat berkonsultasi dengan kode sumber XiangShan, yang telah diterbitkan di bawah MulanPSL2, di GitHub.

sumber: https://www.zhihu.com

Mereka terlalu optimis meskipun masih dalam pengujian dan mengingat fakta bahwa sebagian besar dokumentasi dalam bahasa Cina ketika mereka menemukannya dalam bahasa Inggris. Namun, saya setuju bahwa masa depan adalah RISC-V.