Vor ein paar Tagen das Institut für Informationstechnologie der Chinesischen Akademie der Wissenschaften enthüllt das Projekt XiangShan, in dem es sich seit 2020 entwickelt ein offener Hochleistungsprozessor, der auf der RISC-V (RV64GC)-Befehlssatzarchitektur basiert und dessen Leistung sich der Geschwindigkeit von SiFives neuestem Performance P550-Kern nähert.

Laut den Entwicklern RISC-V-Kerne, die der Xiangshan-CPU zugrunde liegen, werden so beliebt werden unter Entwicklern von Prozessoren wie Linux für Betriebssysteme. Xiangshan wird mit einer 28-nm-Prozesstechnologie von taiwanesischem TSMC hergestellt (es sei denn, die USA verhängen Sanktionen) und dies wird die erste Generation von Kernen mit dem Codenamen Yanqi Lake sein.

RISC-V bietet ein offenes und flexibles Maschinenanweisungssystem die es Ihnen ermöglicht, Mikroprozessoren für beliebige Anwendungen zu erstellen, ohne Lizenzgebühren oder Nutzungsbedingungen zu verlangen. Mit RISC-V können Sie vollständig offene SoCs und Prozessoren erstellen.

Derzeit entwickeln mehrere Unternehmen und Communities auf Basis der RISC-V-Spezifikation unter verschiedenen freien Lizenzen (BSD, MIT, Apache 2.0) mehrere Dutzend Varianten bereits gefertigter Mikroprozessorkerne, SoCs und Chips.

Über XiangShan

Das Projekt wurde unter einer Beschreibung von Hardwareblöcken in der Sprache Chisel veröffentlicht, die in Verilog übersetzt wird, eine Referenzimplementierung basierend auf FPGA und Bildern, um den Betrieb eines Chips in einem offenen Verilog-Simulator zu simulieren.

„Obwohl unser langfristiges Ziel darin besteht, mit [Cortex-] A76 in Einklang zu sein, ist es noch in Arbeit. Wir brauchen eine bodenständige iterative Optimierung. Der Zweck der agilen Entwicklung besteht nicht darin, eine Ecke zu überholen. Die Erfahrungen, die Intel und Arm über die Jahre gesammelt haben, müssen wir auch langsam ansammeln.

Schaltpläne und Architekturbeschreibungen sind ebenfalls verfügbar (insgesamt mehr als 400 Dokumente und 50 Zeilen Code), aber der größte Teil der Dokumentation ist auf Chinesisch, und Debian wird als Referenzbetriebssystem zum Testen der FPGA-Implementierung verwendet.

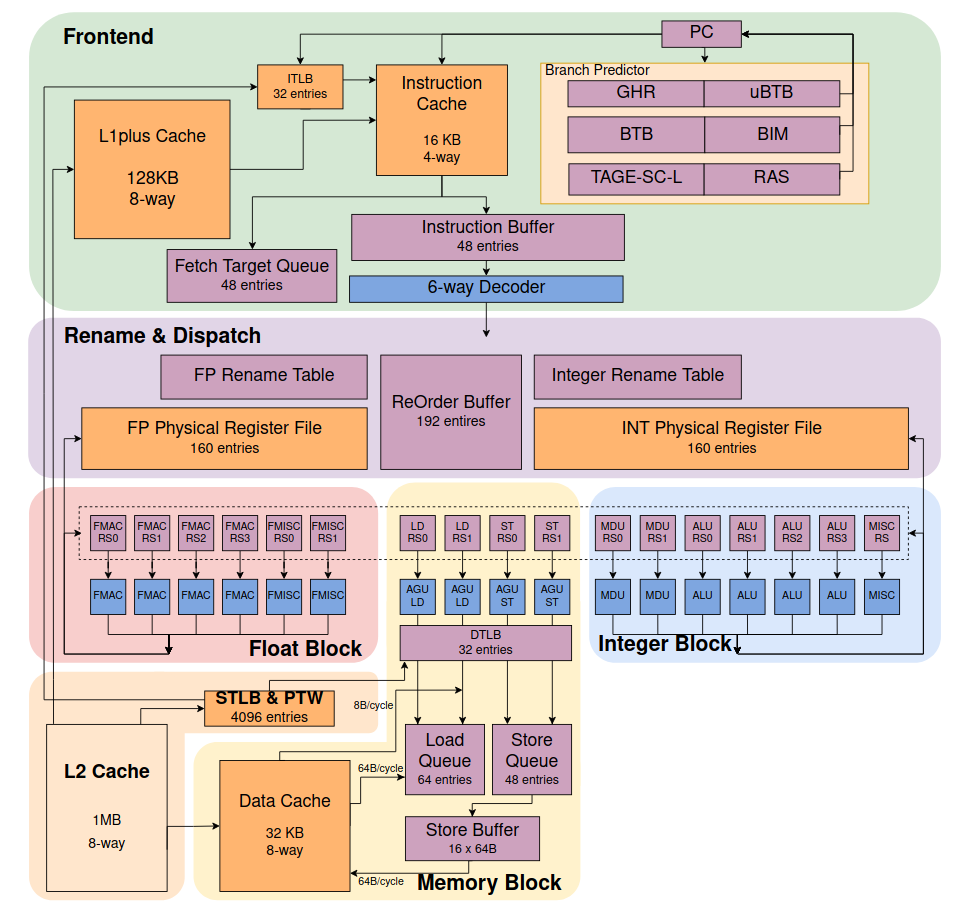

XiangShan behauptet, der leistungsstärkste RISC-V-Chip zu sein, der den SiFive P550 übertrifft. Die FPGA-Tests sollen diesen Monat abgeschlossen werden und der Codename "Yanqi Lake" ist ein 8-Kern-Prototyp-Chip, der mit 1,3 GHz arbeitet und wird bei TSMC mit Verfahrenstechnik von 28 nm.

"Wir hoffen, dass XiangShan 30 Jahre überleben kann", sagte Bao in einer kürzlichen Präsentation des Projekts. „Wir haben eine Vereinbarung, uns in 30 Jahren wieder zu treffen und dann zu sehen, was aus XiangShan wird. Um diesen Wunsch zu verwirklichen, müssen jedoch noch viele Probleme und Herausforderungen gelöst werden.

Der Chip enthält einen 2 MB Cache, ein Speichercontroller mit Unterstützung für DDR4-Speicher (bis zu 32 GB RAM) und eine PCIe-3.0-x4-Schnittstelle.

Die Leistung des ersten Chips im SPEC2006 Benchmark wird auf 7/Ghz geschätzt, was den ARM Cortex-A72 und Cortex-A73 Chips entspricht.

„Der agile Designprozess und die Plattform, die wir zuvor aufgebaut haben, unterstützen ein Entwicklungsteam von mehr als 20 Personen, was bei weitem nicht ausreicht“, sagte Bao. "Was wir jetzt überlegen müssen, ist, wie wir eine Reihe standardisierter, offener und quelloffener Prozesse aufbauen können, die die Entwicklung einer Open-Source-Community von 2000 Menschen unterstützen können."

Die Produktion eines zweiten Prototyps ist für Ende des Jahres geplant "South Lake" mit verbesserter Architektur, die von SMIC mit einer Prozesstechnologie von 14nm und einer Frequenzerhöhung auf 2 GHz produziert wird.

Der zweite Prototyp soll eine Leistung von 10 / Ghz . erreichen auf dem SPEC2006-Benchmark, der nahe an den ARM Cortex-A76- und Intel Core i9-10900K-Prozessoren liegt und den SiFive P550, die schnellste RISC-V-CPU mit 8.65 / Ghz, übertrifft.

Schließlich können Sie, wenn Sie mehr darüber wissen möchten, den Quellcode von XiangShan konsultieren, der unter der MulanPSL2 veröffentlicht wurde, auf GitHub.

Quelle: https://www.zhihu.com

Sie sind zu optimistisch, obwohl es noch getestet wird und die meisten Dokumentationen auf Chinesisch waren, als sie sie auf Englisch fanden. Ich stimme jedoch zu, dass die Zukunft RISC-V sein wird.