Wir haben bereits bei anderen Gelegenheiten über freie Hardware und das opencores.org-Projekt gesprochen, bei dem es viele Open-Source-Chip-Projekte gibt, darunter interessante Mikroprozessoren wie OpenSPARC usw. Nun ist die Firma SiFive hat ein Arduino-kompatibles Entwicklungsboard entwickelt welches einen dieser Chips implementiert. Das macht die Hardware noch offener und es können mehr Eigenschaften des Mikroprozessors bekannt werden, der sie befiehlt.

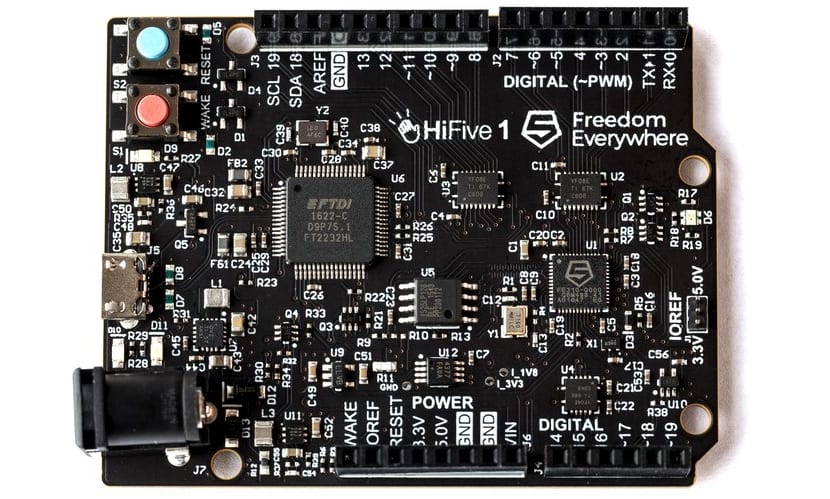

Die Platte aus Beton es heißt HiFive1und sein Hauptmerkmal oder zumindest das auffälligste, da es viele ähnliche oder Arduino-kompatible Karten gibt, ist genau dies, nämlich das Einschließen einer MCU oder einer Mikrocontroller-Einheit mit einer CPU, die auf Open Source ISA RISC-V basiert. Zweifellos gute Nachrichten, und für diejenigen, die diese Art von Projekt noch nicht kennen, empfehle ich Ihnen, auf der opencores.org-Website nachzuforschen, wo Sie alles finden, von Mikroprozessoren, Mikrocontrollern, MMUs, FPUs, ALUs, Speichern usw. alle offenen Projekte unter verschiedenen Lizenzen.

Es scheint, dass die Platte jetzt für etwa 79 US-Dollar verkauft wird und im Januar 59 auf 2017 US-Dollar fallen wird. Der Grund für diese Kreation ist die Neugier von Forschern, Anwendern und Wissenschaftlern, mehr über das Fantastische zu erfahren RISC-V-Architektur. Was ist die Bedeutung dieser Chips, na ja, einfach, es passiert wie zu seiner Zeit bei MIPS oder jetzt bei ARMs, sie sind für Entwickler von großem Interesse und es scheint, dass RISC-V in letzter Zeit speziell das Interesse vieler Gruppen weckt.

RISC und MIPS sind zwei Architekturen, die denjenigen von Ihnen, die mit dieser Welt vertraut sind, bekannt vorkommen, da sie von zwei Personen erstellt wurden, die sich mit Computerarchitekturen am besten auskennen: David Patterson (Universität von Kalifornien) und John Hennessy (Universität in Stanford). Nun können Sie dank des E310-SoC dieser Karte mit einer E31-CorePlex-CPU, einem 32-Bit- und 32-MHz-RV320IMAC-Kern mit 1.61 DMIPs / MHz, hergestellt vom riesigen TMSC, mehr erfahren.