Fa pocs dies l'Institut de Tecnologia Informàtica de l'Acadèmia de Ciències de la Xina va donar a conèixer el projecte Xiangshan, en el qual s'ha estat desenvolupant des del 2020 un processador obert d'alt rendiment basat en l'arquitectura de conjunt d'instruccions RISC-V (RV64GC) i el rendiment dels quals s'acosta a la velocitat de l'últim nucli Performance P550 de SiFive.

Segons els desenvolupadors, els nuclis RISC-V subjacents a la CPU Xiangshan es tornaran tan populars entre els dissenyadors de processadors com ho és Linux per als sistemes operatius. Xiangshan serà fabricat utilitzant una tecnologia de procés de 28 nm per TSMC taiwanès (a menys que els Estats Units imposi sancions) i aquesta serà la primera generació de nuclis amb nom en codi Yanqi Lake.

RISC-V proporciona un sistema d'instrucció de màquina obert i flexible que li permet crear microprocessadors per a aplicacions arbitràries sense requerir regalies o imposar condicions d'ús. RISC-V li permet crear SoC i processadors completament oberts.

Actualment, sobre la base de l'especificació RISC-V, diverses empreses i comunitats sota diverses llicències lliures (BSD, MIT, Apache 2.0) estan desenvolupant diverses dotzenes de variants de nuclis de microprocessadors, SoC i xips ja fabricats.

sobre Xiangshan

El Projecte s'ha publicat sota una descripció de blocs de maquinari en el llenguatge Chisel, Que es tradueix a Verilog, una implementació de referència basada en FPGA i imatges per simular el funcionament d'un xip en un simulador Verilog obert.

«Encara que el nostre objectiu a llarg termini en el futur és estar en línia amb [Cortex-] A76, encara està en progrés. Necessitem una optimització iterativa amb els peus a terra. El propòsit d'el desenvolupament àgil no és avançar una cantonada. L'experiència acumulada per Intel i Arm al llarg dels anys, també hem de acumular-la lentament «.

Els esquemes i les descripcions de l'arquitectura també estan disponibles (Més de 400 documents i 50 mil línies de codi en total), però la major part de la documentació està en xinès, a més que Debian s'utilitza com a sistema operatiu de referència per a provar la implementació de FPGA.

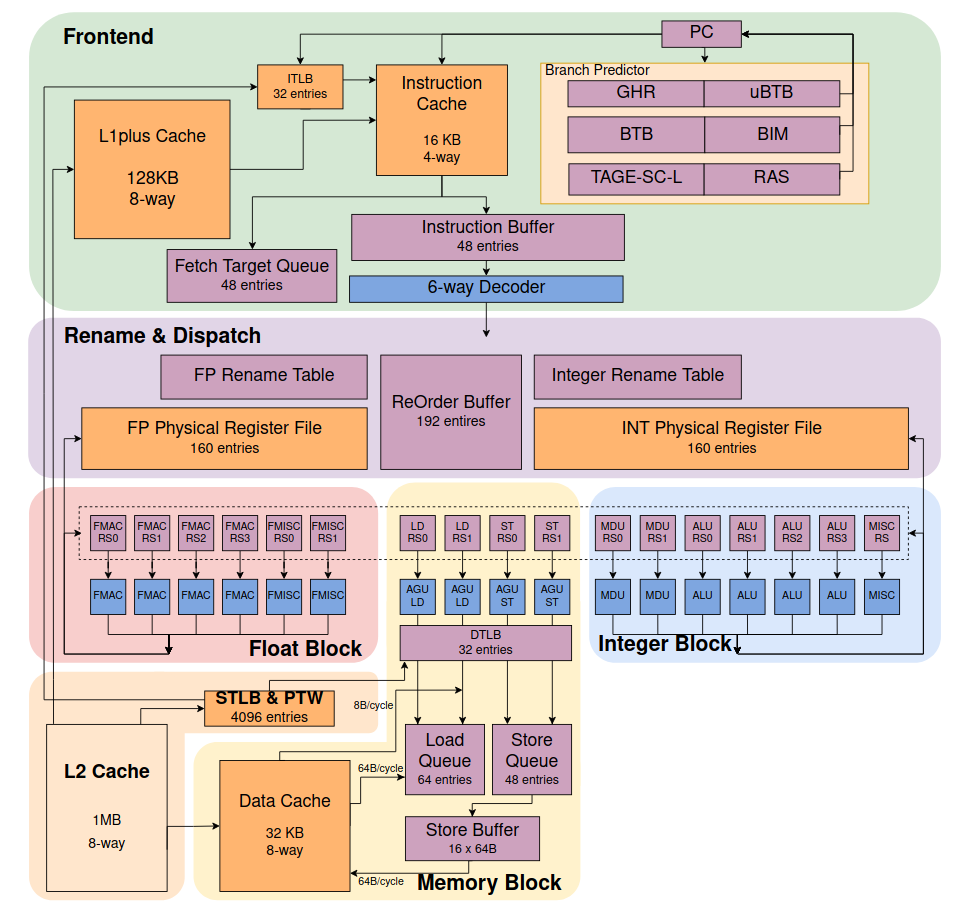

Xiangshan afirma ser el xip RISC-V de major rendiment, superant el SiFive P550. Les proves de FPGA estan programades per completar aquest mes i el nom en codi «Yanqi Lake» és un xip prototip de 8 nuclis que funciona a 1,3 GHz i es fabrica a TSMC utilitzant la tecnologia de procés de 28 nm.

«Tenim l'esperança que Xiangshan pugui sobreviure durant 30 anys», va afirmar Bao, traduït, en una presentació recent sobre el projecte. «Tenim un acord per reunir-nos novament en 30 anys i després veure en què es convertirà Xiangshan. No obstant això, per a realitzar aquest desig, encara hi ha molts problemes i desafiaments que s'han de resoldre ».

el xip inclou una memòria cau de 2 MB, Un controlador de memòria amb suport per a memòria DDR4 (Fins a 32 GB de RAM) i una interfície PCIe-3.0-x4.

El rendiment del primer xip al benchmark SPEC2006 s'estima en 7 / Ghz, que correspon als xips ARM Cortex-A72 i Cortex-A73.

«El procés de disseny àgil i la plataforma que construïm anteriorment donen suport a un equip de desenvolupament de més de 20 persones, el que està lluny de ser suficient», va assenyalar Bao. «El que hem de considerar ara és com construir un conjunt de processos oberts estandarditzats, oberts i de codi obert que puguin donar suport al desenvolupament d'una comunitat de codi obert de 2000 persones».

Per a finals d'any, està prevista la producció d'un segon prototip «South Lake» amb una arquitectura millorada, que serà produït per SMIC amb una tecnologia de procés de 14nm i un augment de freqüència a 2 GHz.

S'espera que el segon prototip abast un rendiment de 10 / Ghz al banc de proves SPEC2006, que està a prop dels processadors ARM Cortex-A76 i Intel Core i9-10900K, i supera el SiFive P550, la CPU RISC-V més ràpida a 8.65 / Ghz.

Finalment si estàs interessat en conèixer més a l'respecte pots consultar el codi font de Xiangshan, el qual s'ha publicat sota la MulanPSL2, a GitHub.

font: https://www.zhihu.com

Són massa optimistes malgrat que encara s'està provant i donat el fet que gairebé tota la documentació està en xinès quan ells la van trobar en anglès. No obstant això, coincideixo amb que el futur serà RISC-V.