قبل بضعة أيام كشف النقاب عن معهد تكنولوجيا المعلومات التابع للأكاديمية الصينية للعلوم المشروع XiangShan ، التي تم تطويرها منذ عام 2020 معالج مفتوح عالي الأداء يعتمد على بنية مجموعة تعليمات RISC-V (RV64GC) والذي يقترب أداؤه من سرعة أحدث نواة P550 من SiFive.

وفقًا للمطورين ، ستصبح نوى RISC-V الأساسية لوحدة المعالجة المركزية Xiangshan شائعة جدًا من بين مصممي المعالجات مثل Linux لأنظمة التشغيل. سيتم تصنيع Xiangshan باستخدام تقنية معالجة 28 نانومتر بواسطة TSMC التايوانية (ما لم يتم فرض عقوبات من قبل الولايات المتحدة) وسيكون هذا الجيل الأول من النوى التي تحمل الاسم الرمزي Yanqi Lake.

RISC-V يوفر نظام تعليمات مفتوح ومرن للآلة يتيح لك إنشاء معالجات دقيقة للتطبيقات التعسفية دون الحاجة إلى الإتاوات أو فرض شروط الاستخدام. يسمح لك RISC-V بإنشاء معالجات SoCs مفتوحة بالكامل.

حاليًا ، استنادًا إلى مواصفات RISC-V ، تقوم العديد من الشركات والمجتمعات بموجب تراخيص مجانية مختلفة (BSD و MIT و Apache 2.0) بتطوير عشرات المتغيرات من نوى المعالجات الدقيقة و SoCs والرقائق المصنعة بالفعل.

حول XiangShan

المشروع تم نشره تحت وصف كتل الأجهزة بلغة الإزميل، والذي تمت ترجمته إلى Verilog ، وهو تطبيق مرجعي يعتمد على FPGA والصور لمحاكاة تشغيل شريحة في محاكي Verilog مفتوح.

"على الرغم من أن هدفنا طويل المدى للمضي قدمًا هو أن نكون متماشيًا مع [Cortex-] A76 ، إلا أنه لا يزال قيد التقدم. نحن بحاجة إلى تحسين تكراري واقعي. الغرض من التطوير السريع ليس تجاوز الزاوية. الخبرة التي تراكمت لدى Intel و Arm على مر السنين ، علينا أيضًا أن نتراكم ببطء.

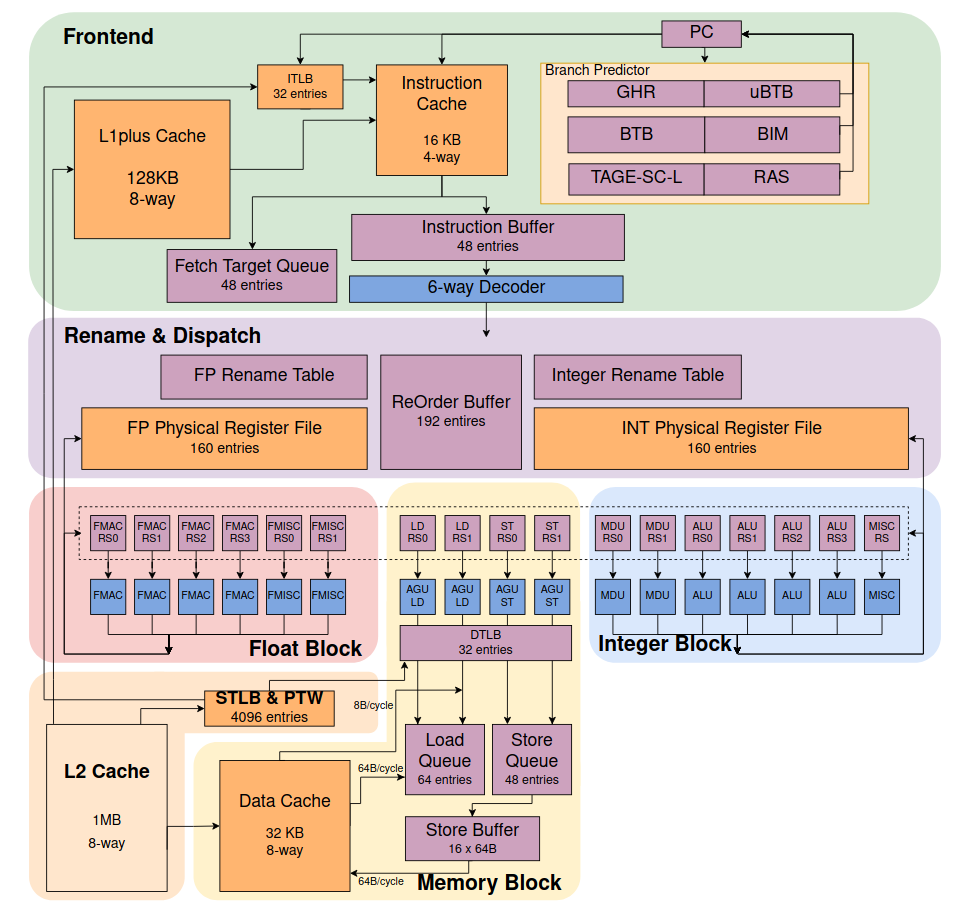

كما تتوفر أوصاف المخططات والعمارة (أكثر من 400 مستند و 50 ألف سطر من التعليمات البرمجية إجمالاً) ، ولكن معظم الوثائق باللغة الصينية ، بالإضافة إلى استخدام دبيان كنظام تشغيل مرجعي لاختبار تطبيق FPGA.

تدعي XiangShan أنها أعلى شريحة RISC-V أداءً ، متفوقةً على SiFive P550. من المقرر أن تكتمل اختبارات FPGA هذا الشهر والاسم الرمزي "بحيرة يانكي" عبارة عن شريحة نموذجية من ثماني نوى تعمل بسرعة 8 جيجاهرتز ويتم تصنيعها في TSMC باستخدام تقنية المعالجة من 28 نانومتر.

قال باو ، في الترجمة ، في عرض تقديمي حديث عن المشروع: "نأمل أن يتمكن XiangShan من البقاء على قيد الحياة لمدة 30 عامًا". "لدينا اتفاق على الاجتماع مرة أخرى في غضون 30 عامًا ثم نرى ما سيصبح XiangShan. ومع ذلك ، لتحقيق هذه الرغبة ، لا يزال هناك العديد من المشاكل والتحديات التي يجب حلها.

رقاقة يتضمن 2 ميغا بايت مخبأ، وحدة تحكم في الذاكرة مع دعم ذاكرة DDR4 (تصل إلى 32 جيجابايت من ذاكرة الوصول العشوائي) وواجهة PCIe-3.0-x4.

يقدر أداء الشريحة الأولى في معيار SPEC2006 بـ 7 / Ghz ، وهو ما يتوافق مع شرائح ARM Cortex-A72 و Cortex-A73.

قال باو: "إن عملية التصميم الرشيقة والمنصة التي أنشأناها سابقًا تدعم فريق تطوير يضم أكثر من 20 شخصًا ، وهو أمر بعيد عن أن يكون كافياً". "ما نحتاج إلى التفكير فيه الآن هو كيفية بناء مجموعة من العمليات مفتوحة المصدر موحدة ومفتوحة المصدر والتي يمكن أن تدعم تطوير مجتمع مفتوح المصدر يضم 2000 شخص."

بحلول نهاية العام ، تم التخطيط لإنتاج نموذج أولي ثانٍ "البحيرة الجنوبية" مع بنية محسنة ، يتم إنتاجها بواسطة SMIC بتقنية معالجة 14 نانومتر وزيادة التردد إلى 2 جيجاهرتز.

من المتوقع أن يحقق النموذج الأولي الثاني أداء 10 / جيجاهرتز وفقًا لمعيار SPEC2006 ، القريب من معالجات ARM Cortex-A76 و Intel Core i9-10900K ، ويتفوق على SiFive P550 ، أسرع وحدة معالجة مركزية RISC-V بسرعة 8.65 / جيجاهرتز.

أخيرًا ، إذا كنت مهتمًا بمعرفة المزيد عنها ، فيمكنك الرجوع إلى الكود المصدري لـ XiangShan ، والذي تم نشره تحت MulanPSL2 ، على جيثب.

مصدر: https://www.zhihu.com

إنهم مفرطون في التفاؤل على الرغم من أنه لا يزال قيد الاختبار وبالنظر إلى حقيقة أن معظم الوثائق مكتوبة بالصينية عندما وجدوها باللغة الإنجليزية. ومع ذلك ، أوافق على أن المستقبل سيكون RISC-V.