شيريوت ، خيار MS للأمان للأنظمة المدمجة

الأخبار مؤخرا كسر ذلك فتحت Microsoft التطورات المتعلقة بمشروع CHERIoT (تمديد أجهزة القدرة إلى RISC-V لإنترنت الأشياء) ، تهدف إلى حظر مشكلات الأمان في كود C و C ++ موجود. تقدم CHERIoT حلاً لحماية قواعد كود C / C ++ الحالية دون الحاجة إلى إعادة بنائها.

يتم تنفيذ الحماية باستخدام مترجم معدل الذي يستخدم مجموعة موسعة خاصة من تعليمات المعالج (ISA) التي يوفرها المعالج ويراقب الوصول إلى الذاكرة على مستوى الأجهزة ، ويتحقق من صحة الوظيفة باستخدام المؤشرات ، ويوفر عزل كتلة التعليمات البرمجية.

حول شيريوت

المشروع تم إنشاؤه على أساس أن الطبيعة منخفضة المستوى للغة C. يصبح مصدرا لأخطاء الذاكرة ، مما يؤدي إلى مشاكل مثل فيضان المخزن المؤقت ، تم تحرير الوصول إلى الذاكرة بالفعل ، أو إلغاء مرجع المؤشر أو التحرير المزدوج.

تُظهر الممارسة أنه حتى الشركات الكبيرة مثل Google و Microsoft ، التي لديها سياسة مراجعة صارمة للتغيير وتستخدم أساليب تطوير حديثة وأدوات تحليل ثابتة ، لا يمكنها ضمان العمل الخالي من الأخطاء مع الذاكرة (على سبيل المثال ، حوالي 70٪ من الثغرات الأمنية في Microsoft و Google ناتجة عن إدارة الذاكرة غير الآمنة).

المشكلة يمكن حلها باستخدام لغات البرمجة التي تضمن العمل الآمن.أو مع ذاكرة أو روابط مع عناصر تحكم إضافية ، على سبيل المثال ، باستخدام MiraclePtr (raw_ptr) بدلاً من المؤشرات الشائعة ، والتي تؤدي عناصر تحكم إضافية للوصول إلى مناطق الذاكرة المحررة.

بيرو هذه الأساليب هي أكثر ملاءمة للكود الجديد y من المزعج للغاية إعادة صياغة مشاريع C / C ++ الحالية ، خاصة إذا كان الغرض منها هو التشغيل في بيئات محدودة الموارد ، مثل الأنظمة المضمنة وأجهزة إنترنت الأشياء.

الكثير تم تصميم مكونات أجهزة CHERIoT كمتحكم دقيق استنادًا إلى بنية RISC-V ، تنفيذ بنية المعالج الآمنة CHERI (ملحق أجهزة السعة لـ RISC-V) ، مما يوفر نموذجًا للوصول إلى الذاكرة المتحكم فيه.

مرتكز على بنية مجموعة التعليمات (هو) تم توفير نموذج برمجة في CHERIoT يضمن أمان العمل مع الذاكرة على مستوى الكائنات الفردية ، ويوفر الحماية ضد الوصول إلى الذاكرة المحررة بالفعل ، وينفذ نظام عزل خفيف الوزن للوصول إلى الذاكرة.

يعكس نموذج الحماية البرمجي هذا نموذج لغة C / C ++ مباشرةً ، مما يسمح باستخدامه لحماية التطبيقات الحالية (مطلوب فقط إعادة الترجمة وتشغيل الأجهزة المتوافقة مع ISA CHERIoT).

يسمح الحل المقترح بمنع الأخطاء التي تسبب خارج حدود الكائن في الذاكرة، لا يسمح باستبدال المؤشر (يجب إنشاء جميع المؤشرات من المؤشرات الموجودة) ، ويراقب الوصول إلى الذاكرة بعد تحريرها (أي وصول إلى الذاكرة بواسطة مؤشر غير صالح أو مؤشر يشير إلى كائن محرّر يثير استثناءً).

على سبيل المثال ، يسمح استخدام CHERIoT ، دون إجراء أي تغييرات في التعليمات البرمجية ، بتنفيذ فحص تلقائي للحدود ، وتتبع عمر مناطق الذاكرة ، وضمان سلامة المؤشرات في المكونات التي تعالج البيانات غير الموثوق بها.

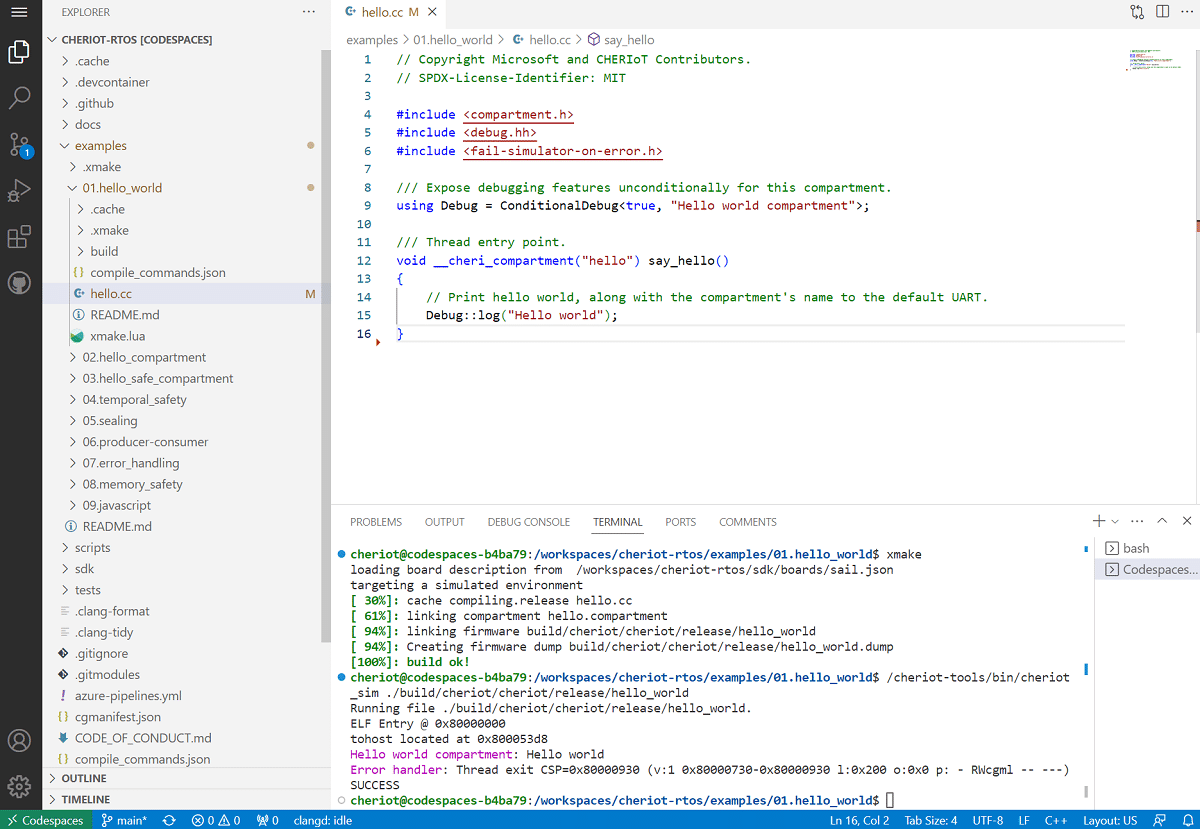

المشروع يتضمن مواصفات لهندسة مجموعة تعليمات CHERIoT التمديد ، تطبيق مرجعي لوحدة المعالجة المركزية RISC-V المتوافقة مع ISA CHERIoT 32 بت ، ومجموعة أدوات LLVM معدلة.

أخيرا إذا كنت مهتمًا بمعرفة المزيد عنها ، يجب أن تعلم أن مخططات النماذج الأولية يتم توزيع أوصاف كتلة وحدة المعالجة المركزية والأجهزة في Verilog بموجب ترخيص Apache 2.0. يتم استخدام جوهر Ibex لمشروع lowRISC كأساس لوحدة المعالجة المركزية ويتم تحديد نموذج رمز CHERIoT ISA بلغة الشراع ويتم توزيعه بموجب ترخيص BSD.

بالإضافة إلى ذلك ، تم اقتراح نموذج أولي لنظام التشغيل في الوقت الحقيقي CHERIoT RTOS ، والذي يوفر القدرة على عزل الأجزاء (المقصورة) حتى على الأنظمة المضمنة مع 256 ميجابايت من ذاكرة الوصول العشوائي.

الرمز شيريوت رتوس إنه مكتوب بلغة C ++ ويتم توزيعه بموجب ترخيص MIT. في شكل مقصورات ، تم تصميم المكونات الأساسية لنظام التشغيل ، مثل أداة تحميل التمهيد ، وجدولة ، ونظام تخصيص الذاكرة.