Il ya quelques jours l'Institut des technologies de l'information de l'Académie chinoise des sciences dévoilé le projet XiangShan, dans laquelle il se développe depuis 2020 un processeur ouvert hautes performances basé sur l'architecture du jeu d'instructions RISC-V (RV64GC) et dont les performances approchent la vitesse du dernier cœur Performance P550 de SiFive.

Selon les développeurs, Les cœurs RISC-V sous-jacents au processeur Xiangshan deviendront si populaires parmi les concepteurs de processeurs tels que Linux pour les systèmes d'exploitation. Xiangshan sera fabriqué à l'aide d'une technologie de processus de 28 nm par le taïwanais TSMC (sauf si des sanctions sont imposées par les États-Unis) et ce sera la première génération de cœurs portant le nom de code Yanqi Lake.

RISC-V fournit un système d'instruction machine ouvert et flexible qui vous permet de créer des microprocesseurs pour des applications arbitraires sans exiger de redevances ni imposer de conditions d'utilisation. RISC-V vous permet de créer des SoC et des processeurs complètement ouverts.

Actuellement, sur la base de la spécification RISC-V, plusieurs sociétés et communautés sous diverses licences libres (BSD, MIT, Apache 2.0) développent plusieurs dizaines de variantes de cœurs de microprocesseurs, SoC et puces déjà fabriqués.

À propos de Xiang Shan

Le projet a été publié sous une description des blocs matériels dans le langage Chisel, qui est traduit en Verilog, une implémentation de référence basée sur FPGA et images pour simuler le fonctionnement d'une puce dans un simulateur Verilog ouvert.

"Bien que notre objectif à long terme soit d'être en ligne avec [Cortex-] A76, il est toujours en cours. Nous avons besoin d'une optimisation itérative terre-à-terre. Le développement agile n'a pas pour but de prendre un virage. L'expérience accumulée par Intel et Arm au fil des ans, nous devons aussi l'accumuler lentement.

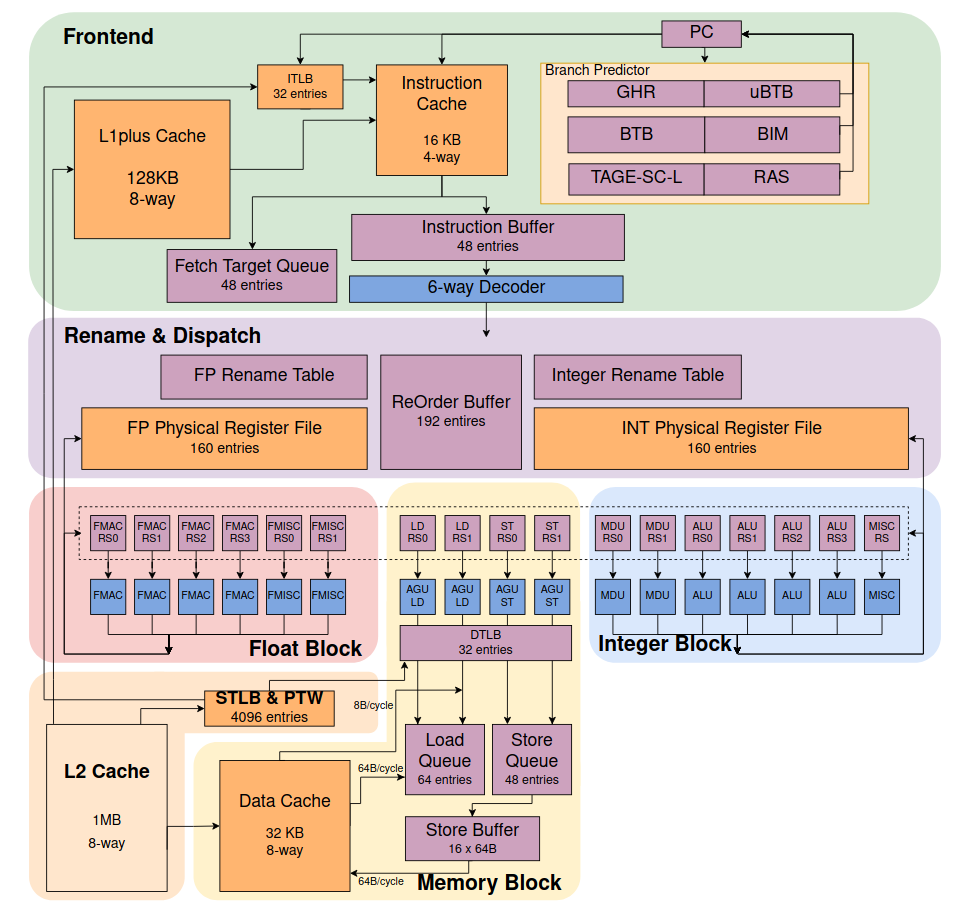

Des schémas et des descriptions d'architecture sont également disponibles (plus de 400 documents et 50 XNUMX lignes de code au total), mais la plupart de la documentation est en chinois, et Debian est utilisé comme système d'exploitation de référence pour tester l'implémentation du FPGA.

XiangShan prétend être la puce RISC-V la plus performante, surpassant la SiFive P550. Les tests FPGA devraient être terminés ce mois-ci et le nom de code "Yanqi Lake" est un prototype de puce à 8 cœurs qui fonctionne à 1,3 GHz et est fabriqué à TSMC en utilisant la technologie de processus de 28 nm.

"Nous espérons que XiangShan pourra survivre pendant 30 ans", a déclaré Bao, traduit, dans une récente présentation sur le projet. « Nous avons un accord pour nous revoir dans 30 ans et voir ensuite ce que deviendra XiangShan. Cependant, pour réaliser ce souhait, de nombreux problèmes et défis doivent encore être résolus.

La puce comprend un cache de 2 Mo, un contrôleur de mémoire avec prise en charge de la mémoire DDR4 (jusqu'à 32 Go de RAM) et une interface PCIe-3.0-x4.

Les performances de la première puce du benchmark SPEC2006 sont estimées à 7/Ghz, ce qui correspond aux puces ARM Cortex-A72 et Cortex-A73.

"Le processus de conception agile et la plate-forme que nous avons construits précédemment prennent en charge une équipe de développement de plus de 20 personnes, ce qui est loin d'être suffisant", a déclaré Bao. "Ce que nous devons considérer maintenant, c'est comment créer un ensemble de processus open source standardisés, ouverts et open source qui peuvent soutenir le développement d'une communauté open source de 2000 XNUMX personnes."

La production d'un deuxième prototype est prévue pour la fin de l'année "South Lake" avec une architecture améliorée, qui sera produit par SMIC avec une technologie de processus de 14 nm et une augmentation de fréquence à 2 GHz.

Le deuxième prototype devrait atteindre une performance de 10/Ghz sur le benchmark SPEC2006, qui est proche des processeurs ARM Cortex-A76 et Intel Core i9-10900K, et surpasse le SiFive P550, le processeur RISC-V le plus rapide à 8.65 / Ghz.

Enfin, si vous souhaitez en savoir plus, vous pouvez consulter le code source de XiangShan, qui a été publié sous le MulanPSL2, sur GitHub.

source: https://www.zhihu.com

Ils sont trop optimistes même s'il est encore en cours de test et compte tenu du fait que la plupart de la documentation est en chinois alors qu'ils l'ont trouvée en anglais. Cependant, je suis d'accord que l'avenir sera RISC-V.